You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Assertion Synthesisby Paul McLellan on 08-28-2012 at 2:46 pmCategories: EDA

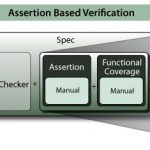

In June, Atrenta acquired NextOp, the leader in assertion synthesis. So what is it?

Depending on who you ask, verification is a huge fraction, 60-80%, of the cost of an SoC design, so obviously any technology that can reduce the cost of verification has a major impact on the overall cost and schedule of a design. At a high-level, verification… Read More

Increasingly the challenge with SoCs, especially for mobile, is not getting the performance high enough but doing so in a power-efficient manner. Handheld devices running multiple apps need high-speed processors that consume extremely low levels of power both in operating and standby modes. In the server farm, the limit is … Read More

All semiconductor companies were caught up in ASIC in some way or another because of the basic economics. Semiconductor technology allowed medium sized designs to be done, and medium sized designs were pretty much all different. The technology didn’t yet allow whole systems to be put on a single chip. So semiconductor companies… Read More

When I worked for virtual platform companies, one of the things that I used to tell prospective customers was that virtual prototypes were not some second-rate approach to software and hardware development to be dropped the moment real silicon was available, that in many ways they were better than the real hardware since they had… Read More

Synopsys announced their results today. With Magma rolled in (but not yet SpringSoft since that hasn’t technically closed) they had revenue of $443M up 15% from $387M last year. This means that they are all but a $1.75B company and a large part of the entire EDA industry (which I think of as being $5B or so, depending on just what… Read More

Cadence at 20nmby Paul McLellan on 08-21-2012 at 8:10 pmCategories: Cadence, EDA

Cadence has a new white paper out about the changes in IC design that are coming at 20nm. One thing is very clear: 20nm is not simply “more of the same”. All design, from basic standard cells up to huge SoCs has several new challenges to go along with all the old ones that we had at 45nm and 28nm.

I should emphasize that the paper… Read More

In the early 1980s the ideas and infrastructure for what would eventually be called ASIC started to come together. Semiconductor technology had reached the point that a useful number of transistors could be put onto a chip. But unlike earlier, when a chip only held a few transistors and thus could be used to create basic generic building… Read More

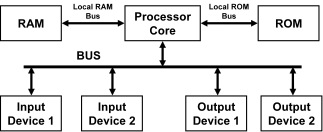

It is obviously a truism that somewhere in an SoC there is something limiting a further increase in performance. One area where this is especially noticeable is when a Tensilica core is used to create a highly optimized processor for some purpose. The core performance may be boosted by a factor of 10 or even as much as 100. Once the core… Read More

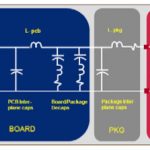

One of the really big changes about chip design is the way over the last decade or so it is no longer possible to design an SoC, a package for it to go in and the board for the package using different sets of tools and methodologies and then finally bond out the chip and solder it onto the board. The three systems, Chip-Package-System have… Read More

Tomorrow night in Sunnyvale at the National Institute of Technology Alumni meeting, Ajoy Bose and Jim Hogan will talk about different aspects of SoC Realization. I’ve been saying for some time that design is changing and the block level is really where the action is. That is the right level to put together a virtual platform… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era