I am not making this up: All exports from the United States of EDA software and services are controlled under the Export Administration Regulations, administered by the U.S. Department of Commerce’s Bureau of Industry and Security (BIS). You need to understand these regulations. Failure to comply can result in severe … Read More

Author: Paul McLellan

Are 28nm Transistors the Cheapest…Forever?

It is beginning to look as if 28nm transistors, which are the cheapest per million gates compared to any earlier process such as 45nm, may also be the cheapest per million gates compared to any later process such as 20nm.

What we know so far: FinFET seems to be difficult technology because of the 3D structure and so the novel manufacturing… Read More

TSMC’s 16FinFET and 3D IC Reference Flows

Today TSMC announced three reference flows that they have been working on along with various EDA vendors (and ARM and perhaps other IP suppliers). The three new flows are:

- 16FinFET Digital Reference Flow. Obviously this has full support for non-planar FinFET transistors including extraction, quantized pitch placement, low-vdd

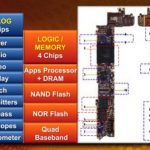

How to Design an LTE Modem

Designing an LTE modem is an interesting case study in architectural and system level design because it is pretty much on the limit of what is possible in a current process node such as 28nm. I talked to Johannes Stahl of Synopsys about how you would accomplish this with the Synopsys suite of system level tools. He is the first to admit… Read More

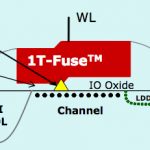

Sidense and TSMC Processes

I’ve written before about the basic capabilities of Sidense’s single transistor one-time programmable memory products (1T-OTP). Just to summarize, it is an anti-fuse device that works by permanently rupturing the gate oxide under the bit-cells storage transistor, something that is obviously irreversible.… Read More

Back To The Future: 50th Anniversary of EDA

October 16[SUP]th[/SUP] at the Computer History Museum, EDAC is hosting EDA: Back to the Future to celebrate 50 years of EDA. EDAC always has a fall event of some sort and historically it has been the Kaufman Award Dinner. This year, the Kaufman Award was presented (to Chenming Hu) at 50[SUP]th[/SUP] DAC, so the fall EDAC calendar… Read More

Intel Quark: Synthesizable Core?

At IDF Brian Krzanich gave the keynote. I won’t summarize the whole thing here but just talk about one part that was something they had actually managed to keep secret ahead of time: Quark.

Quark is a synthesizable core. It uses 1/10th power of Atom and is 1/5 size. Now I am writing this, I don’t know if this is a fair comparison… Read More

GlobalFoundries Expands in Singapore

GlobalFoundries has been in Singapore for a long time. Longer than GlobalFoundries has existed in fact. Chartered Semiconductor was started in Singapore in 1987 and GF acquired them in early 2010 less than a year after they were created by spinning out the manufacturing arm of AMD. When GF was started their state of the art fab was… Read More

Cadence Introduces Palladium XP II

Well, despite all the arguments in the blogosphere about what process node palladium’s silicon is, and whether the design team is competent, and why it reports into sales…Cadence has announced their latest big revision of Palladium. Someone seems to be able to get things done. Of course it is bigger and faster and … Read More

TSMC OIP: Mentor’s 5 Presentations

At TSMC’s OIP on October 1st, Mentor Graphics have 5 different presentations. Collect the whole set!

11am, EDA track. Design Reliability with Calibre Smartfill and PERC. Muni Mohan of Broadcom and Jeff Wilson of Mentor. New methodologies were invented for 28nm for smart fill meeting DFM requirements (and at 20nm me may … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center