You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Yesterday I met with David Hsu who is the marketing guy for Synopsys’s cloud computing solution that they announced at their user-group meeting earlier this year. It was fun to catch up; David used to work for me back in VLSI days although he was an engineer writing place and route software back then.

David admits that this is… Read More

There are various rumors around about Cadence starting to close up stuff that has been open for a long time. Way back in the midst of time, as part of the acquisition of CCT, the Federal Trade Commission forced Cadence to open up LEF/DEF and allow interoperability of Cadence tools (actually only place and route) I believe for 10 years.… Read More

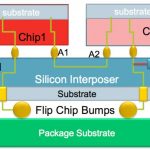

Going up! Power and performance issues, along with manufacturing yield issues, limit how much bigger chips can get in two dimensions. That, and the fact that you can’t manufacture two different processes on the same wafer, mean that we are going up into the third dimension.

The simplest way is what is called package-in-package… Read More

The CEO panel at the 2nd GTC wasn’t especially enlightening. The theme was that going forward will require cooperation for success and everyone was really ready to cooperate.

The most interesting concept was Aart talking about moving from what he called “scale complexity” aka Moore’s law to what he … Read More

I went to the second Global Technology Conference yesterday. It started with a keynote by Ajit Manocha who is the CEO of about 2 months. I hadn’t realized until someone asked him during the press lunch that he is technically only the “acting” CEO. Actually, given his experience he might be the right person anyway,… Read More

Analog has always been difficult, a bit of a black art persuading a digital process to create well-behaved analog circuits, capacitors, resistors and all the rest. In the distant past, we would solve this by putting the analog on a separate chip, often in a non-leading-edge process. But modern SoCs integrate large amounts of digital… Read More

Mentor has transferred its Catapult (high level synthesis) product line, including the people, to Calypto. Terms were not disclosed but apparently it is a non-cash deal. Calypto gets the product line. Mentor gets a big chunk of ownership of Calypto. So maybe the right way to look at this is as a partial acquisition of Calypto.

It … Read More

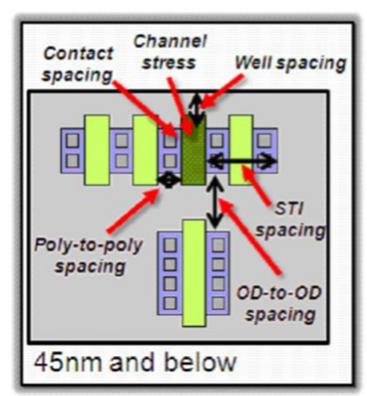

20nm SoC Designby Paul McLellan on 08-25-2011 at 12:48 amCategories: Uncategorized

There are a large number of challenges at 20nm that didn’t exist at 45nm or even 32nm.

The biggest issues are in the lithography area. Until now it has been possible to make a reticle using advanced reticle enhacement technology (RET) decoration and have it print. Amazing when you think that at 45nm we are making 45nm features… Read More

OK, let’s face it, when you think of post-silicon debug then formal verification is not the first thing that springs to mind. But once a design has been manufactured, debugging can be very expensive. As then-CEO of MIPS John Bourgoin said at DesignCon 2006, “Finding bugs in model testing is the least expensive and most desired… Read More

Silicon Oneby Paul McLellan on 08-23-2011 at 5:23 pmCategories: Uncategorized

I have talked quite a bit over the last few years about how the trend towards small consumer devices with very fast ramp times. For example, pretty much any time Apple introduces a new product line (iPod, iPhone, iPad…) it becomes the fastest growing market in history. This has major implications for semiconductor design … Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era