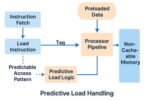

When people talk about bottlenecks in digital signal processors (DSPs), they usually focus on compute throughput: how many MACs per second, how wide the vector unit is, how fast the clock runs. But ask any embedded AI engineer working on always-on voice, radar, or low-power vision—and they’ll tell you the truth: memory stalls … Read More

Author: Jonah McLeod

Predictive Load Handling: Solving a Quiet Bottleneck in Modern DSPs

Even HBM Isn’t Fast Enough All the Time

Why Latency-Tolerant Architectures Matter in the Age of AI Supercomputing

High Bandwidth Memory (HBM) has become the defining enabler of modern AI accelerators. From NVIDIA’s GB200 Ultra to AMD’s MI400, every new AI chip boasts faster and larger stacks of HBM, pushing memory bandwidth into the terabytes-per-second range. … Read More

RISC-V’s Privileged Spec and Architectural Advances Achieve Security Parity with Proprietary ISAs

Because of its open and modular nature, RISC-V has faced recognizable security challenges stemming from fragmentation, performance inefficiencies, and inherent vulnerabilities. Fragmentation across implementations leads to inconsistencies, making it difficult to enforce uniform security measures. Performance… Read More

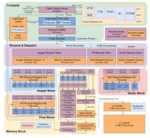

Harnessing Modular Vector Processing for Scalable, Power-Efficient AI Acceleration

The dominance of GPUs in AI workloads has long been driven by their ability to handle massive parallelism, but this advantage comes at the cost of high-power consumption and architectural rigidity. A new approach, leveraging a chiplet-based RISC-V vector processor, offers an alternative that balances performance, efficiency,… Read More

An Open-Source Approach to Developing a RISC-V Chip with XiangShan and Mulan PSL v2

As RISC-V gains traction in the global semiconductor industry, developers are exploring fully open-source approaches to processor design. XiangShan, a high-performance RISC-V CPU project, combined with the Mulan Permissive License v2 (Mulan PSL v2), represents a community-driven, transparent alternative to proprietary… Read More

Solving the EDA tool fragmentation crisis