SoC designs frequently have lots of different clock domains to help manage power more efficiently, however one side effect is that when the clock domains meet, i.e., in a Clock Domain Crossing (CDC), there’s the possibility of setup and hold time violations that can cause a flip-flop to become metastable. Synchronizer … Read More

Author: Daniel Payne

Handling metastability during Clock Domain Crossing (CDC)

New STA Features from Cadence

Static Timing Analysis (STA) has been an EDA tool category for many years now, yet with each new generation of smaller foundry process nodes come new physical effects that impact timing, requiring new analysis features to be added. For advanced process nodes, there are five different types of analysis that must be included when… Read More

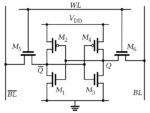

Webinar: Fast and Accurate High-Sigma Analysis with Worst-Case Points

IC designers are tasked with meeting specifications like robustness in SRAM bit cells where the probability of a violation are lower than 1 part-per-billion (1 ppb). Another example of robustness is a Flip-Flop register that must have a probability of specification violation lower than 1 part-per-million (1 ppm). Using Monte… Read More

SRAM design analysis and optimization

Every year EDA vendor MunEDA hosts a user group meeting where engineers present how they used automation tools to improve their IC designs, and one presentation from Peter Huber of Infineon caught my attention, it was all about SRAM design optimization. Peter has authored papers at IEEE conferences and been issued patents related… Read More

Managing IP, Chiplets, and Design Data

Design re-use has enabled IC design teams to create billion-transistor designs where hundreds of IP blocks are pre-built from internal or external sources. Keeping track of where each of these IP blocks came from, what their version status is, managing IP, or even discerning their license status can be a full-time job if tracked… Read More

An Update on IP-XACT standard 2022

Semiconductor IP design re-use has enabled the relentless growth in complexity of SoC and chiplet-based systems over the years, and with IP reuse comes many unique challenges. Fabless design companies use IP provided by a vibrant ecosystem of IP suppliers and foundries, plus internal re-use in the quest to get to market more … Read More

TSMC N3E is ready for designs, thanks to IP from Synopsys

TSMC has been offering foundry services since 1987, and their first 3nm node was called N3 and debuted in 2022; now they have an enhanced 3nm node dubbed N3E that has launched. Every new node then requires IP that is carefully designed, characterized and validated in silicon to ensure that the IP specifications are being met and … Read More

AI for the design of Custom, Analog Mixed-Signal ICs

Custom and Analog-Mixed Signal (AMS) IC design are used when the highest performance is required, and using digital standard cells just won’t meet the requirements. Manually sizing schematics, doing IC layout, extracting parasitics, then measuring the performance only to go back and continue iterating is a long, tedious… Read More

Version Control, Data and Tool Integration, Collaboration

As a follow up from my #60DAC visit with Simon Rance of Keysight I was invited to their recent webinar, Unveiling the Secrets to Proper Version Control, Seamless Data and Tool Integration, and Effective Collaboration. Karim Khalfan, Director of Solutions Engineering, Data & IP Management was the webinar presenter.

Modern… Read More

Power Analysis from Software to Architecture to Signoff

SoC designs use many levels of design abstraction during their journey from ideation to implementation, and now it’s possible to perform power analysis quite early in the design process. I had a call with William Ruby, Director of Porduct Marketing – Synopsys Low Power Solution to hear what they’ve engineered… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?