You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Most SoCs today are being prototyped in FPGA hardware before committing to costly IC fabrication. You could just design and build your own FPGA prototyping system, or instead choose something off the shelf and then concentrate on your core competence of SoC design.

Thanks to the FPGA vendors like Xilinx we now have FGPA prototyping… Read More

The tremendous growth in IC and SoC design complexity has now enabled engineers to place bilions of transistors on a single chip. To make that growth possible design teams resort to using libraries and semi IP provided by other groups in their company, or outside IP vendors. To lower risk, you must know that the IP being used in your… Read More

There’s a one-person EDA start-up called iSchematics.com that offers schematic capture and cloud-based simulation for both web browsers and mobile devices like the iPhone and iPad that is being sued. I’ve blogged about their EDA tools before:

…

Read More

Analog design seems to suffer from a huge gap when it comes to testing and verification. While some of this gap is natural – after all, often the only way to verify whether a particular design is working is to look at actual simulation waveforms – it still seems like a lot can be done to bring process into this sphere of the… Read More

Analog and Mixed-Signal (AMS) designers are facing more challenges than ever, so where can they go to get some relief? One place is a half-day seminar scheduled for May 16th in Bridgewater, New Jersey. SemiWiki has teamed up with Tanner EDA, Abbot Labs and SoftMEMS to present topics of:

- True collaborative design enabled through

…

Read More

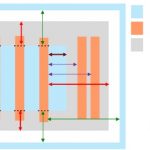

IC designers involved with physical design are familiar with acronyms like DRC (Design Rule Check), LVS (Layout Versus Schematic) and DFM (Design For Manufacturing), but how would you go about checking for compliance with ESD (Electro Static Discharge) rules? You may be able to kludge something together with your DRC tool and… Read More

Designing at the 20nm node is harder than at 28nm, mostly because of the lithography and process variability challenges that in turn require changes to EDA tools and mask making. The attraction of 20nm design is realizing SoCs with 20 billion transistors. Saleem Haider from Synopsys spoke with me last week to review how Synopsys… Read More

Speed, capacity, accuracy – these are the three major EDA tool metrics that we pay attention to and that enable us to design and verify an SoC. Talk to any design or verification engineer and ask if they are satisfied with the time that it takes to simulate their latest design, or to verify that it meets spec and is functionally… Read More

We’ve blogged before about Layout Dependent Effects (LDE) on SemiWiki and how it further complicates the IC design and layout process, especially at 28nm and lower nodes because the IC layout starts to change the MOS device performance. There’s an interesting webinarfrom Cadence on Variation-aware IC Design, … Read More

Foundries and EDA vendors are cooperating at increasing levels of technical intimacy as we head to the 20nm and lower nodes. Cadence has a strong position in the EDA tools used for IC design and layout of custom and AMS (Analog Mixed-Signal) designs. They have created a series of webinars to highlight the design challenges and new… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!