I first met Dundar Dumlugolat Barcelona Design back in 2004, so it was a pleasure to meet with him again at DAClast week and learn more about what his company Magwel has to offer IC designers of power management chips.… Read More

Author: Daniel Payne

MEMS Update from DAC

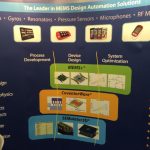

DAC has an interesting mix of vendors each year, and some of them are outside of the expected digital, analog or IP space. Last Tuesday at DAC I visited a company called Coventor that has three product lines:

- MEMS+ – MEMS design and analysis tools

- CoventorWare – Modeling and simulation for MEMS devices

- SEMulator 3D–

An Update on Calibre at DAC

Even though I live just 7 miles away from the Mentor Graphics corporate office in Oregon, I visited their DAC suite in San Francisco last week to get an update on Calibrefrom Michael White. The Calibre tools are used during IC verification and sign-off by performing DRC (Design Rule Checking) and LVS (Layout Versus Schematic).… Read More

IoT Breakfast Panel at DAC

Tuesday morning at DAC I enjoyed a free breakfast courtesy of Synopsysand GLOBALFOUNDRIESwhere I learned more about the emerging market of IoT, and what it means to semiconductor, EDA and IP vendors. Panelists included: Semico Research, HP, Synopsys, GLOBALFOUNDRIES and Broadcom. … Read More

High Sigma Yield Analysis and Optimization at DAC

When I hear the phrase “high sigma” I think of the EDA vendor Solido, however at DAC on Monday I visited another EDA company called MunEDAthat has several products of interest to transistor-level IC designers. I was able to speak with three different people from MunEDA and here’s what I learned.… Read More

AMS Panel: Micronas, Infineon, AMD, STMicro

Synopsyshosted an AMS Luncheon panel today at DACin the Westin Hotel and invited four customers to talk about their actual design challenges and experiences. I’ve typed up my notes from this event.… Read More

Affordable AMS EDA Tools at DAC

First thing at DACtoday I met with Greg Lebsack of Tanner EDA to ask about what’s new in the past year for his EDA company. Here are my meeting notes, so there’s not much prose for my DAC blogs this year.

… Read More

Gary Smith at DAC

Gary Smith once again wore his signature white coat and extolled the virtues of system level design and automation. The room at the Intercontinental was packed, and the folks in the hallway outside were noisy as usual, eager for the party to start after Gary finished.… Read More

Active Power Management in UPF Using SPICE, VHDL-AMS or Verilog-AMS

My former co-worker, Kenneth Bakalar at Mentor Graphics is an expert in AMS modeling languages and UPFmethodology, so he recently teamed up with Eric Jeandeau to author an interesting white paper: Interpreting UPF for a Mixed-Signal Design Under Test. This white paper is based on a presentation made at DVCon earlier this year.… Read More

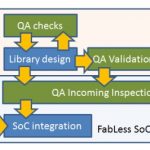

How About a Quality-Aware IP Design Flow

In the EDA world we use hyphens quite often to describe our technical approaches, like: DFM-aware, Power-aware, Variation-aware. I just read a white papertoday on the topic of Quality-Aware IP Design Flows, written by Fractal Technologies. If your group creates IP or re-uses IP, then there’s always the question about … Read More

Tesla and Samsung Relationship Update