PwC’s comprehensive report, “Semiconductor and Beyond,” released in 2026, provides a strategic outlook on the global semiconductor industry amid rapid transformations driven by AI, geopolitical tensions, and supply chain shifts. Structured into four sections—Foreword, Demand Analysis, Supply Analysis,… Read More

Author: Admin

Global Semiconductor Industry Outlook 2026

Advancing Semiconductor Design: Intel’s Foveros 2.5D Packaging Technology

In the rapidly evolving landscape of semiconductor manufacturing, the demand for processors that handle increasing workloads while maintaining power efficiency and compact form factors has never been higher. Intel’s Foveros 2.5D packaging technology emerges as a pivotal innovation, enabling denser die integration… Read More

Smart Verification for Complex UCIe Multi-Die Architectures

By Ujjwal Negi – Siemens EDA

Multi-die architectures are redefining the limits of chip performance and scalability through the integration of multiple dies into a single package to deliver unprecedented computing power, flexibility, and efficiency. At the heart of this transformation is the Universal Chiplet Interconnect… Read More

Revolutionizing Processor Design: Intel’s Software Defined Super Cores

In the ever-evolving landscape of computing, Intel’s patent application for “Software Defined Super Cores” (EP 4 579 444 A1) represents a groundbreaking approach to enhancing processor performance without relying solely on hardware scaling. Filed in November 2024 with priority from a U.S. application… Read More

TSMC’s 2024 Sustainability Report: Pioneering a Greener Semiconductor Future

TSMC, the world’s most trusted semiconductor foundry, released its 2024 Sustainability Report, underscoring its commitment to embedding environmental, social, and governance principles into its operations. Founded in 1987 and headquartered in Hsinchu Science Park, TSMC employs 84,512 people globally and operates… Read More

Intel’s Commitment to Corporate Responsibility: Driving Innovation and Sustainability

Introduction by Lip-BU Tan:

I’m an engineer at heart. Nothing motivates me more than solving hard problems. Our teams across Intel are driven by this same mindset—inspired by the power of technology to enable new solutions to our customers’ toughest challenges.

I fundamentally believe this will be a catalyst for innovation throughout… Read More

Cadence’s Strategic Leap: Acquiring Hexagon’s Design & Engineering Business

In a bold move that underscores the accelerating convergence of electronic design automation (EDA) and mechanical engineering, Cadence Design Systems announced its agreement to acquire Hexagon AB’s Design & Engineering (D&E) business for approximately €2.7 billion, equivalent to about $3.16 billion. This… Read More

Beyond Von Neumann: Toward a Unified Deterministic Architecture

By Thang Tran

For more than half a century, the foundations of computing have stood on a single architecture: the Von Neumann or Harvard model. Nearly all modern chips—CPUs, GPUs, and even many specialized accelerators—rely on some variant of this design. Over time, the industry has layered on complexity and specialization to… Read More

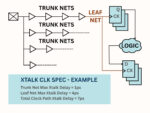

Static Timing Analysis Signoff – A comprehensive and Robust Approach

By Zameer Mohammed

Once a chip is taped out, changes in design are not possible – Silicon is unforgiving, does not allow postproduction modifications. In contrast, software can be updated after release, but chips remain fixed. Static Timing Analysis (STA) signoff serves as a crucial safeguard against silicon failures.

In modern… Read More

eBook on Mastering AI Chip Complexity: Pathways to First-Pass Silicon Success

The rapid evolution of artificial intelligence (AI) is transforming industries, from autonomous vehicles to data centers, demanding unprecedented computational power and efficiency. As highlighted in Synopsys’ guide, the global AI chip market is projected to reach $383 billion by 2032, growing at a 38% CAGR. This … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center