How Time-Based Scheduling

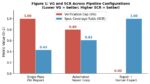

Reclaims Silicon Wasted by Speculative Execution

By: Dr. Thang Tran, Founder and CTO, Simplex Micro

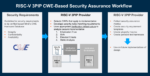

I have spent my career designing processor architectures, and I have reached an uncomfortable conclusion: a substantial fraction of the silicon area and power in modern high-performance processors… Read More

Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed Sea