Dan is joined by sureCore CEO Paul Wells. Paul has worked in the semiconductor industry for over 25 years including two years as director of engineering for Pace Networks, where he led a multidisciplinary, 70 strong product development team creating a broadcast quality video & data mini-headend. Before that, he worked for… Read More

With over 30 years of diverse industry experience, Darin leads SILICET, a semiconductor IP licensing firm. He spearheaded a strategic pivot to focus on a seamless LDMOS innovation that delivers unmatched cost, performance and reliability advantages – backed by a robust global patent portfolio. Prior to co-founding SILICET,… Read More

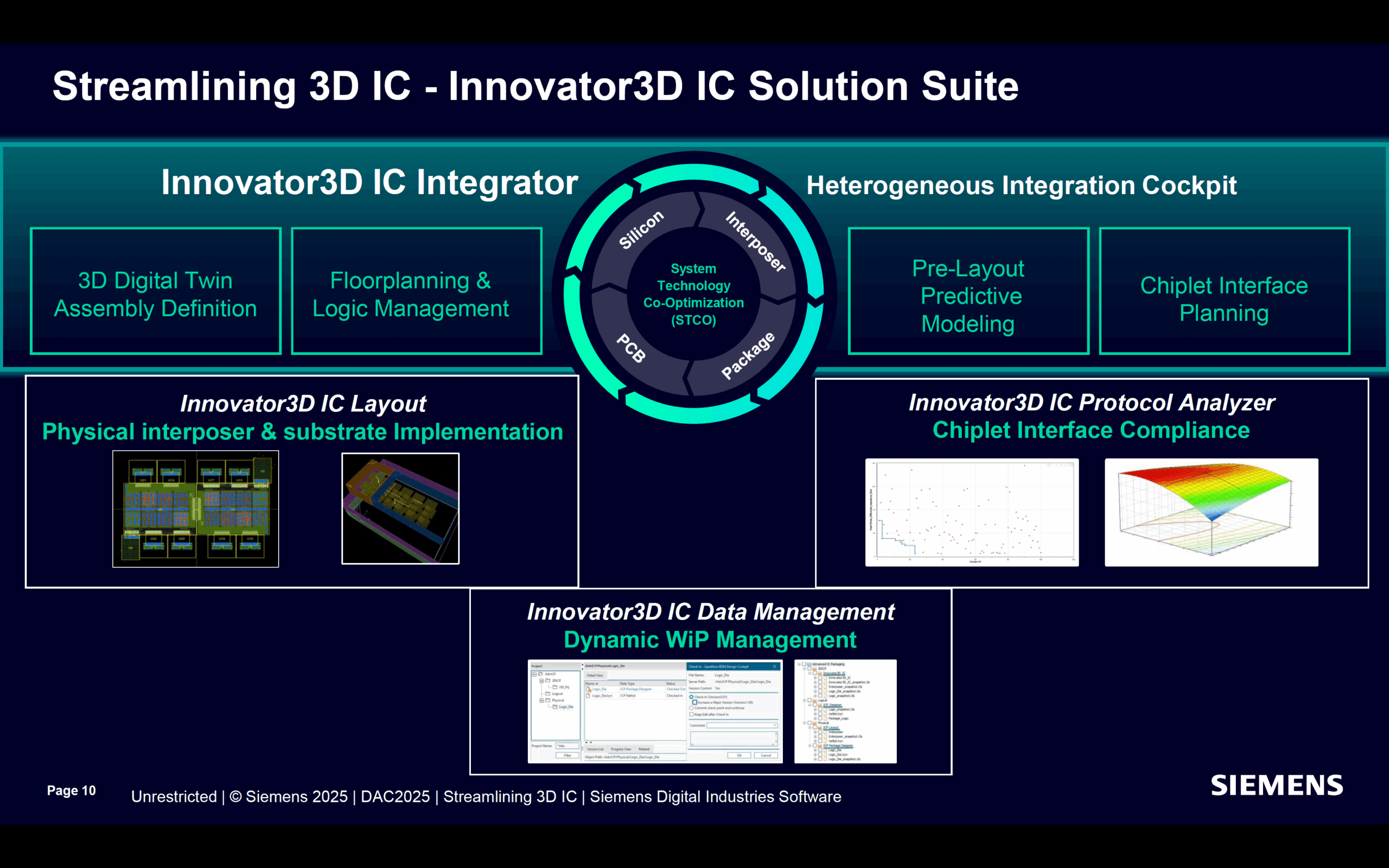

The semiconductor industry is rapidly moving beyond traditional 2D packaging, embracing technologies such as 3D integrated circuits (3D ICs) and 2.5D advanced packaging. These approaches combine heterogeneous chiplets, silicon interposers, and complex multi-layer routing to achieve higher performance and integration.… Read More

AI explosion is clearly driving semi-industry since 2020. AI processing, based on GPU, need to be as powerful as possible, but a system will reach optimum only if it can rely on top interconnects. The various sub-system need to be interconnected with ever more bandwidth and lower latency, creating the need for ever advanced protocol… Read More

AI technology was prevalent at DAC 2025, but can we really trust what Generative AI (GenAI) is producing? Vishal Moondhra, VP of Solutions Engineering from Perforce talked about this topic in the Exhibitor Forum on Monday, so I got a front row seat to learn more.

Vishal started out by introducing the four challenges and risks of using… Read More

Dan is joined by Dr. Tiffany Callahan from SandboxAQ. As one of the early movers in the evolving sciences of computational biology, machine learning and artificial intelligence, Tiffany serves as the technical lead for agentic and autonomous systems at SandboxAQ. She has authored over 50 peer-reviewed publications, launched… Read More

In AI it is easy to be distracted by hype and miss the real advances in technology and adoption that are making a difference today. Accellera hosted a panel at DAC on just this topic, moderated by Dan Nenni (Mr. SemiWiki). Panelists were: Chuck Alpert, Cadence’s AI Fellow driving cross-functional Agentic AI solutions throughout… Read More

In the race to deliver ever-larger SoCs under shrinking schedules, simulation is becoming a bottleneck. With debug cycles constrained by long iteration times—even for minor code changes—teams are finding traditional flows too rigid and slow. The problem is further magnified in continuous integration and continuous deployment… Read More

Many know Arteris as the “network-on-chip”, or NoC, company. Through acquisitions and forward-looking development, the footprint for Arteris has grown beyond smart interconnect IP. At DAC this year, Arteris highlighted its latest expansion with a new SoC integration automation product called Magillem Packaging. The announcement… Read More

Last month, Lj Ristic delivered an invited talk on MEMS technology as a driving force at the Laser Display and Lighting Conference 2025, held at Trinity College Dublin. His talk included a review of some major successes of MEMS industry. We used that occasion to talk to him and discuss some major achievements and the status of MEMS… Read More

Facing the Quantum Nature of EUV Lithography