This year’s live semiconductor ecosystem conferences have been well attend and I expect the same for #61DAC next week. I will be at the conference from Sunday afternoon to Wednesday evening, if you would like to meet let me know. Networking is an important part of the semiconductor ecosystem so let’s make it happen.

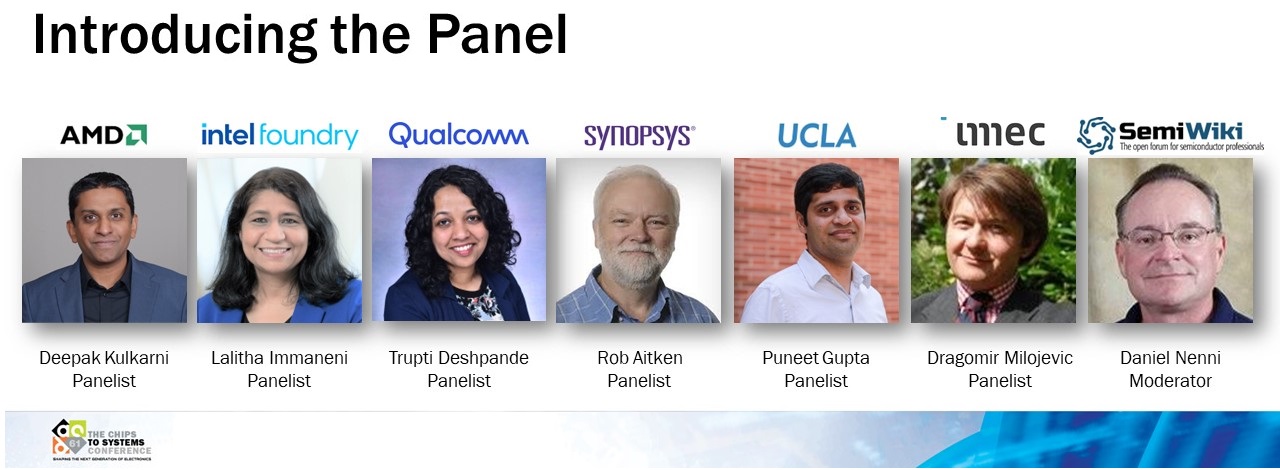

The final opportunity to meet me at #61DAC will be on Wednesday afternoon. I will be moderating a panel on 3DIC, one of the more popular topics on SemiWiki.

3DIC Design Ecosystem – The Cats That Need Herding!

At the end of 2D scaling of Moore’s law, 3D integrated circuits that take advantage of advanced packaging and heterogeneous integration offers many prospects of extending the chip density scaling and the system performance improvements for the next decade. Much of 3DIC design activity in the industry today is done via different teams within the same company. 3DICs hold the potential to not only make the chip architecture heterogeneous, but also chiplet sourcing to be highly diversified. Moreover, 3DICs themselves have a few avenues to be realized towards commercial success, ranging from true disaggregated chiplets to sequential stacked processing. This presses us to answer a few key questions:

1. Technology:

a. How will heat dissipation be managed, are new cooling techniques being pursued to mitigate the thermal challenges?

b. How to design the power delivery network from the board to the substrate to the multi-tier of 3D stack with minimal voltage drop and high-power conversion efficiency? How to design the backside power delivery in leading edge node CMOS with 3D stacking?

c. How to ensure signal integrity, yield and reliability between multiple tiers of 3D stacking, and what testing and standardization efforts are needed to embrace the heterogeneous dies from different designers and different foundries?

2. EDA flows and interoperability

a. Will the ecosystem extend the same standards-based interoperability of design tools, flows and methodologies to 3DIC, as enjoyed by system designers today?

b. How can the EDA industry help system designers in planning, managing and tracking their complex 3DIC projects in implementation, analysis, and signoffs?

3. Roadmap:

a. Is the roadmap to sequential monolithic stacked 3DIC inevitable? What factors will lead the industry to it?

b. What are the boundaries between monolithic 3D integration (with sequential processing at BEOL) and heterogenous 3D integration (with die stacking or bonding)?

We as an industry must be able to apply lessons from the past struggles with monolithic chip design and interoperability to this emerging challenge. This panel will discuss the need, scope of solution, and potential candidate efforts already in motion.

I hope to see you there!

Also Read:

Breker Verification Systems at the 2024 Design Automation Conference

Flex Logix at the 2024 Design Automation Conference

Alphacore at the 2024 Design Automation Conference

Share this post via:

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center