Overview

SerDes (short for Serializer/Deserializer) is a high-speed circuit block used to convert parallel data to serial form and back again. It is widely used in integrated circuits, networking equipment, SoCs, and interconnect protocols to enable high-bandwidth data transmission over limited pin or channel resources.

SerDes technology is foundational to modern high-speed interfaces such as PCI Express (PCIe), Ethernet, USB, SATA, DisplayPort, JESD204, and chiplet interconnects (e.g., UCIe, BoW).

🔧 Purpose and Functionality

A SerDes system includes two main components:

-

Serializer – Converts wide parallel data into a narrow high-speed serial stream.

-

Deserializer – Converts the serial stream back into parallel data at the receiver end.

Why SerDes is Important:

-

Reduces the number of required I/O pins and wires.

-

Minimizes signal skew and routing complexity.

-

Enables transmission over high-speed links with low power.

🏗️ SerDes Architectures

1. Parallel SerDes (Simplex)

-

Used for unidirectional communication.

-

Example: HDMI transmitter.

2. Full Duplex SerDes

-

Supports simultaneous transmit and receive.

-

Used in most high-speed network interfaces (Ethernet, PCIe).

3. Source-Synchronous SerDes

-

Clock transmitted alongside data (e.g., DDR, older SerDes).

4. Clock-Embedded SerDes (Clock Recovery)

-

Receiver extracts clock from serial stream using CDR (Clock and Data Recovery).

-

Used in PCIe, USB, Ethernet, etc.

⚙️ Key SerDes Parameters

| Parameter | Description |

|---|---|

| Data Rate | Speed of transmission (e.g., 10 Gbps, 112 Gbps) |

| Latency | Delay introduced by serialization and deserialization |

| Jitter | Timing variation in signal transitions |

| Bit Error Rate (BER) | Ratio of error bits to total transmitted |

| Pre-emphasis / Equalization | Signal conditioning to maintain eye opening at receiver |

| CDR (Clock & Data Recovery) | Enables receiver to align sampling with incoming data |

🧠 SerDes in Protocols

| Protocol | SerDes Role |

|---|---|

| PCIe Gen 1–6 | Uses SerDes for bidirectional high-speed lanes |

| Ethernet (10G/25G/100G/400G) | Uses SerDes-based physical layer (PHY) for optical/copper links |

| SATA/SAS | Serial data transport for storage |

| USB 3.x/4 | Uses SerDes with Type-C connector and DP Alt mode |

| DisplayPort, HDMI | Multimedia SerDes transmission |

| JESD204B/C | High-speed serial links between ADCs/DACs and FPGAs/SoCs |

| UCIe, BoW, XSR, AIB | SerDes-based chiplet interconnect standards |

🛠️ Design Considerations

On-Die vs. PHY IP

-

SerDes can be integrated as custom hard IP blocks in ASIC/SoC designs.

-

Leading SerDes IP vendors provide:

-

Full custom PHYs (Analog + DSP)

-

Multi-rate support

-

Process-portable options (from 28nm to 3nm and below)

-

Power vs. Performance Tradeoff

-

High-speed SerDes consume significant power.

-

Low-power SerDes variants are critical for mobile, edge, and AI applications.

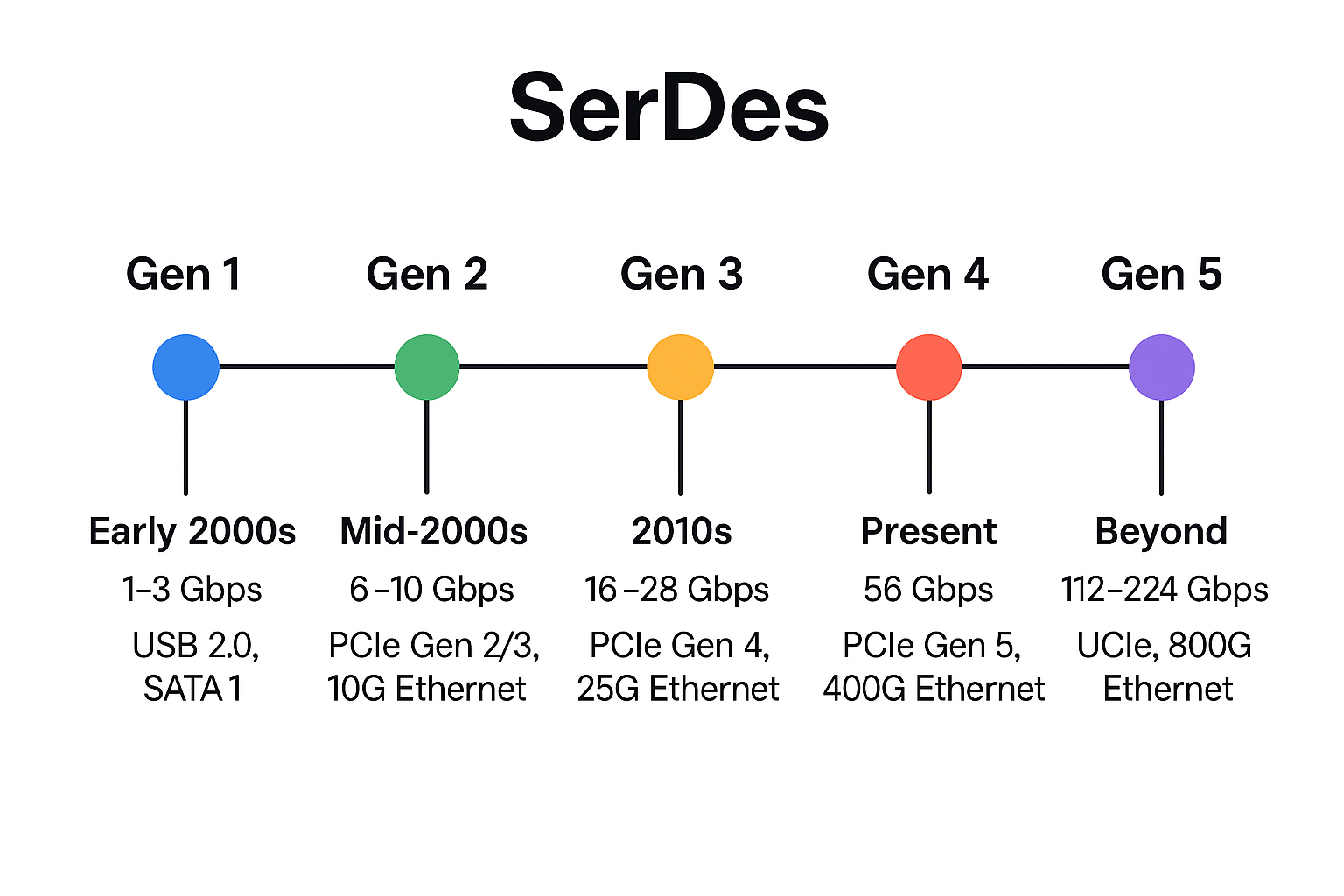

📈 Evolution and Generations

| Generation | Data Rate | Application |

|---|---|---|

| Gen 1 (early 2000s) | 1–3 Gbps | USB 2.0, SATA 1 |

| Gen 2 (mid-2000s) | 6–10 Gbps | PCIe Gen 2/3, 10G Ethernet |

| Gen 3 | 16–28 Gbps | PCIe Gen 4, 25G Ethernet, JESD204B |

| Gen 4 | 56 Gbps | PCIe Gen 5, 100G Ethernet, SerDes for AI |

| Gen 5 (current) | 112 Gbps | PCIe Gen 6, 400G/800G Ethernet |

| Gen 6 (in development) | 224 Gbps | UCIe 2.0, 1.6Tbps Ethernet, future chiplet links |

🌐 Key SerDes IP Vendors

| Company | Notes |

|---|---|

| Synopsys | Industry leader in PHY IP for PCIe, Ethernet, USB, UCIe |

| Alphawave Semi | Specializes in 56G/112G SerDes for AI/HPC/datacenter |

| Cadence | Offers SerDes IP and PHYs (USB4, PCIe, 112G) |

| Rambus | High-speed memory and SerDes PHY IP |

| Credo, eSilicon (Inphi) | Optical SerDes PHY IP, CPO |

| Siemens EDA | Offers simulation and verification of SerDes systems |

| AnalogX, Kandou, Marvell | Focused on ultra-low-power or chiplet-centric SerDes designs |

🔬 Applications

-

AI/ML Accelerators: SerDes enables chiplet-to-chiplet and die-to-die connections.

-

Automotive Ethernet: High-speed serial links in ADAS and infotainment.

-

5G Infrastructure: Baseband and fronthaul/backhaul transport via SerDes.

-

Datacenter Networking: 400G and 800G Ethernet switch-to-server links.

-

Consumer Electronics: Display (DP, HDMI), USB, storage, and camera interfaces.

🧭 Future Trends

| Trend | Impact |

|---|---|

| Chiplet architectures | High-bandwidth, low-power SerDes IP required |

| 112G–224G SerDes | Enabling terabit-scale networking |

| Co-Packaged Optics (CPO) | SerDes to optical transceiver integration |

| Die-to-Die PHYs | Short-reach, ultra-efficient SerDes for 3D ICs |

| AI-optimized DSP | Adaptive equalization and channel learning in real time |

CEO Interview with Jerome Paye of TAU Systems