Overview

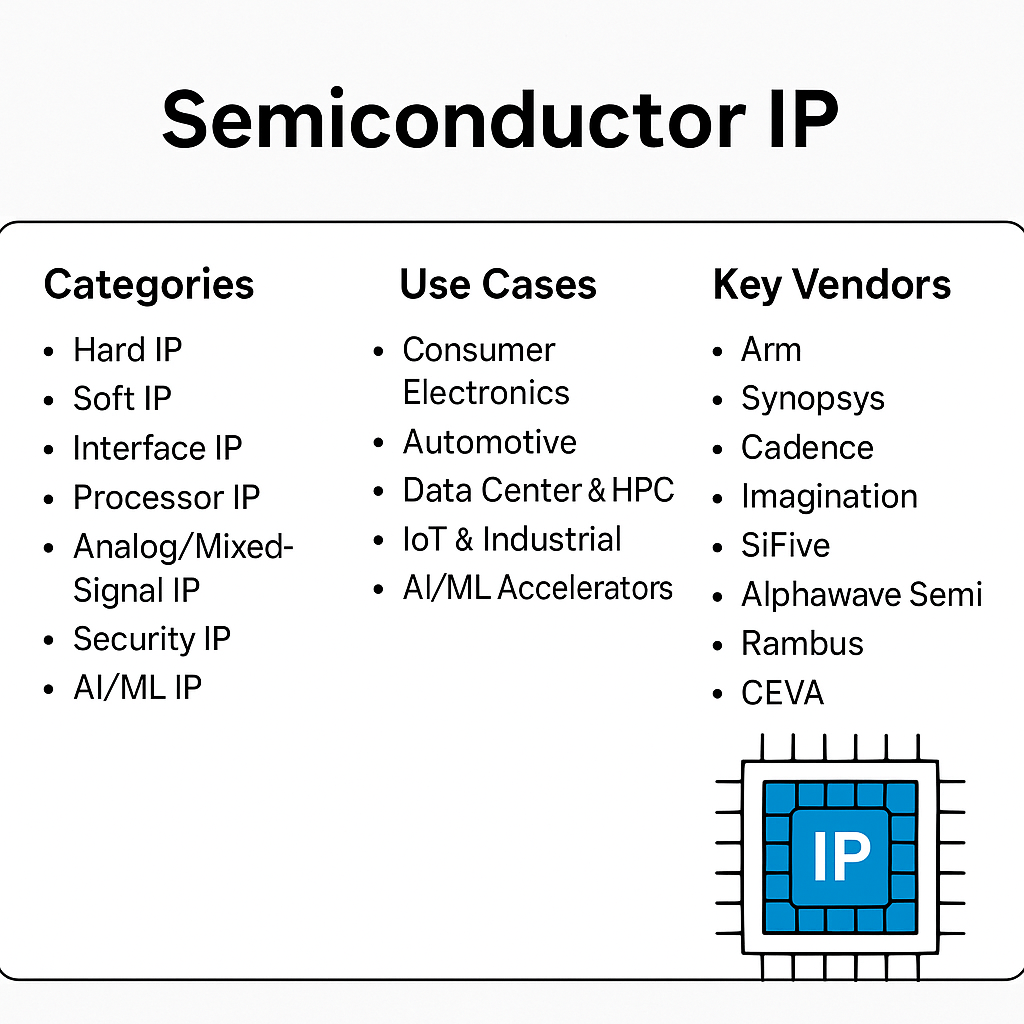

Semiconductor IP refers to pre-designed, reusable blocks of logic, circuits, or software that are licensed for integration into larger system-on-chip (SoC), ASIC, or FPGA designs. These building blocks accelerate development, reduce cost, and allow semiconductor designers to focus on differentiation rather than reinventing core technologies.

Semiconductor IP can range from simple logic cells to complex processors and interfaces like CPU cores, memory controllers, PHYs, AI engines, and security blocks. The industry has evolved into a multi-billion-dollar ecosystem with leading IP vendors playing a critical role in chip design innovation.

🧱 Types of Semiconductor IP

| Category | Examples | Description |

|---|---|---|

| Hard IP | Analog PHYs, SerDes | Pre-placed, fully routed layouts; process-specific |

| Soft IP | CPU cores, DSPs | Synthesizable RTL code; portable across nodes |

| Firm IP | SRAM blocks | Optimized netlists; some layout guidance provided |

| Interface IP | PCIe, USB, DDR, MIPI, HDMI | Standard I/O protocols, PHY + controller |

| Processor IP | Arm, RISC-V, DSP cores | Central processing units and subsystems |

| Analog/Mixed-Signal IP | PLLs, ADCs, DACs | For timing, clocking, power management |

| Security IP | Hardware crypto engines, PUFs | Implements encryption, authentication, root-of-trust |

| AI/ML IP | NPU, matrix accelerators | Optimized for AI workloads on edge and datacenter devices |

💡 Use Cases

Semiconductor IP is used across:

-

Consumer electronics (smartphones, wearables)

-

Automotive (ADAS, infotainment)

-

Data center & HPC

-

IoT & industrial devices

-

AI/ML accelerators

-

Networking & storage controllers

Example: A smartphone SoC integrates dozens of IPs: Arm CPU, GPU, LPDDR PHY, PCIe controller, USB, ISP, neural processor, and more.

🧬 IP Lifecycle

| Phase | Details |

|---|---|

| Design | IP is developed, verified, and characterized by the vendor |

| Validation | Must pass silicon validation (e.g., test chips, compliance testing) |

| Licensing | Customer licenses IP for SoC integration |

| Integration | IP is incorporated into SoC using design tools (EDA flows) |

| Verification | IP is validated in context of full chip design |

| Tapeout & Silicon | Chip goes to fabrication; IP vendor supports debug if needed |

🏢 Key IP Vendors

| Company | Key IP Products |

|---|---|

| Arm | CPU (Cortex), GPU (Mali), interconnects |

| Synopsys | Interface IP (USB, PCIe, DDR), analog IP, ARC processors |

| Cadence (Tensilica) | DSPs, AI processors, SerDes |

| Imagination Technologies | GPU (PowerVR), neural processors |

| SiFive | RISC-V CPU IP |

| Alphawave Semi | SerDes, DSPs |

| Rambus | Memory and interface IP |

| CEVA | DSP, AI/ML IP |

| Arteris | Network-on-Chip (NoC) IP |

| Secure-IC, PQShield, CryptoNext | Cryptography and quantum-safe IP |

Emerging companies like Esperanto, Menta, Codasip, Axiomise, and OpenFive also contribute specialized or open-source IP.

💰 Business Models

| Model | Description |

|---|---|

| One-time license fee | Upfront cost for a specific design use |

| Royalty-based | Vendor earns per-chip royalty (e.g., cents per unit) |

| Subscription/Access | Time-limited access to IP portfolio |

| Multi-project licensing | For use in multiple chips or product families |

📈 Market Size and Trends

-

The global semiconductor IP market was valued at $6–7 billion (2023).

-

Expected to reach $10+ billion by 2030, driven by:

-

SoC complexity

-

Shorter time-to-market

-

Chiplet design and die-to-die IP

-

Custom silicon trends (e.g., from hyperscalers)

-

Key trends:

-

Shift to RISC-V: Open instruction set architecture driving new CPU IP markets.

-

AI and ML IP: Neural Processing Units (NPUs) growing rapidly.

-

Chiplets and 3D ICs: Demand for die-to-die PHY IP and high-speed SerDes.

-

Automotive-grade IP: ISO 26262-compliant IP needed for ADAS and EVs.

🧪 IP Verification and Standards

-

IP must be validated for performance, timing, area, and power (PPA).

-

Compliance with standards like JEDEC, PCI-SIG, USB-IF, MIPI Alliance.

-

IP vendors often submit test chips or FPGA demos for certification.

-

Tools for formal verification, functional simulation, and SoC integration:

-

Synopsys VCS, Cadence Xcelium, Siemens Questa

-

🔒 Security and Quality Considerations

-

Hardware Trojans or IP vulnerabilities can affect the entire SoC.

-

IP must comply with functional safety (ISO 26262) and cybersecurity standards (e.g., NIST, SESIP).

-

IP lifecycle increasingly includes post-quantum cryptography and side-channel attack resistance.

🧠 Open Source IP

The rise of open-source hardware IP is led by:

-

RISC-V Foundation: Open CPU ISA with growing ecosystem (SiFive, Andes, Codasip)

-

CHIPS Alliance: Promotes open IP cores, tools, and methodologies

-

OpenHW Group: Focused on verification and quality of open IP

-

OpenTitan: Google’s open secure root-of-trust IP

Open IP faces challenges in commercial validation, tool support, and compliance, but is rapidly maturing.

🧭 Future Outlook

| Trend | Impact |

|---|---|

| Chiplet-based design | Increases demand for die-to-die IP (e.g., UCIe, BoW) |

| AI at the edge | Drives need for compact, energy-efficient AI IP blocks |

| Automotive & safety | Certification-ready IP becomes a competitive differentiator |

| Quantum-safe IP | Integration of lattice-based cryptography and secure boot |

| 3D IC & advanced packaging | IP must be co-optimized for thermal and integration specs |

Semiconductor IP Examples

🧱 1. Processor IP

| IP Type | Examples | Description |

|---|---|---|

| CPU IP | Arm Cortex, RISC-V (SiFive, Andes), Synopsys ARC | General-purpose compute cores |

| DSP IP | Cadence Tensilica, CEVA-X, Synopsys EV, Arm Helium | Optimized for signal processing |

| GPU IP | Arm Mali, Imagination PowerVR, Vivante | Graphics and visual computing |

| NPU / AI IP | Cadence DNA, CEVA NeuPro, Arm Ethos | For ML inference, neural networks |

| Secure CPU | Crypto processors, OpenTitan, PUF-based | Hardware root of trust and crypto engines |

🔌 2. Interface IP

| Protocol | Providers | Notes |

|---|---|---|

| PCIe (Gen 3–6) | Synopsys, Cadence, Alphawave, Rambus | High-speed I/O |

| USB (2.0–4.0) | Synopsys, Cadence, Arasan | Universal peripheral I/O |

| Ethernet (1G–800G) | Synopsys, Rambus, Credo | Networking PHYs and MACs |

| DDR/LPDDR (3–5X) | Rambus, Synopsys, Cadence | Memory interfaces |

| HDMI / DisplayPort | Synopsys, Silion Image | Display video interfaces |

| MIPI (CSI, DSI, I3C) | Synopsys, Arasan, Mixel | Imaging and mobile interfaces |

| UCIe / BoW / XSR | Alphawave, Synopsys, E-Fuse | Chiplet and die-to-die links |

🧮 3. Memory IP

| Type | Examples |

|---|---|

| SRAM / ROM / TCAM | Arm Artisan, Synopsys, Silvaco |

| Non-Volatile Memory (NVM) | EEPROM, Flash, OTP from eMemory, Kilopass |

| HBM/DDR PHY IP | Rambus, Alphawave, Cadence |

| Secure Memory | Tamper-resistant RAM, PUF-based OTP |

🔋 4. Analog / Mixed-Signal IP

| IP Type | Description |

|---|---|

| PLL / DLL | Timing, frequency synthesis |

| ADC / DAC | Data conversion for sensors/audio |

| SerDes PHY | Serializer/Deserializer blocks for high-speed links |

| PMIC IP | Voltage regulators, LDOs, power sequencing |

| Clocking IP | Low jitter oscillators and spread-spectrum clocks |

🔒 5. Security IP

| Feature | Examples |

|---|---|

| Crypto Engines | AES, SHA, RSA, ECC IP from Secure-IC, Rambus |

| TRNG / PUF | True Random Number Generator, Physical Unclonable Function |

| Secure Boot / Fuse | Root-of-trust and key management |

| Post-Quantum IP | Lattice-based crypto cores (e.g., PQShield, CryptoNext) |

🎥 6. Video / Imaging IP

| Function | Providers |

|---|---|

| ISP (Image Signal Processor) | Arm Mali-C, Synopsys EV6x |

| Video Codec IP | H.264/H.265, AV1, VP9 from Imagination, Cadence |

| Sensor Interface | MIPI CSI/DSI with timing + lane management |

🧠 7. AI/ML Accelerator IP

| Vendor | Core |

|---|---|

| Cadence | DNA AI Engine |

| Arm | Ethos-N |

| CEVA | NeuPro / SensPro |

| Synopsys | ARC NPX |

| Imagination | NNA, AXE family |

🧰 8. Design Infrastructure IP

| Type | Description |

|---|---|

| Standard Cell Libraries | Logic gates, flip-flops (Arm Artisan, Synopsys) |

| IO Libraries | ESD-protected, high-voltage IO cells |

| Memory Compilers | Automatic SRAM/ROM generator IP |

| NoC (Network-on-Chip) | Arteris, NetSpeed (Intel) |

Things From Intel 10K That Make You Go …. Hmmmm