Term: Network-on-Chip (NoC)

Also Known As: On-chip Interconnect Network, SoC Interconnect Fabric

Domain: Semiconductor Architecture, System-on-Chip (SoC), Multiprocessor Design

Primary Use: Communication backbone for multi-core processors, SoCs, and chiplets

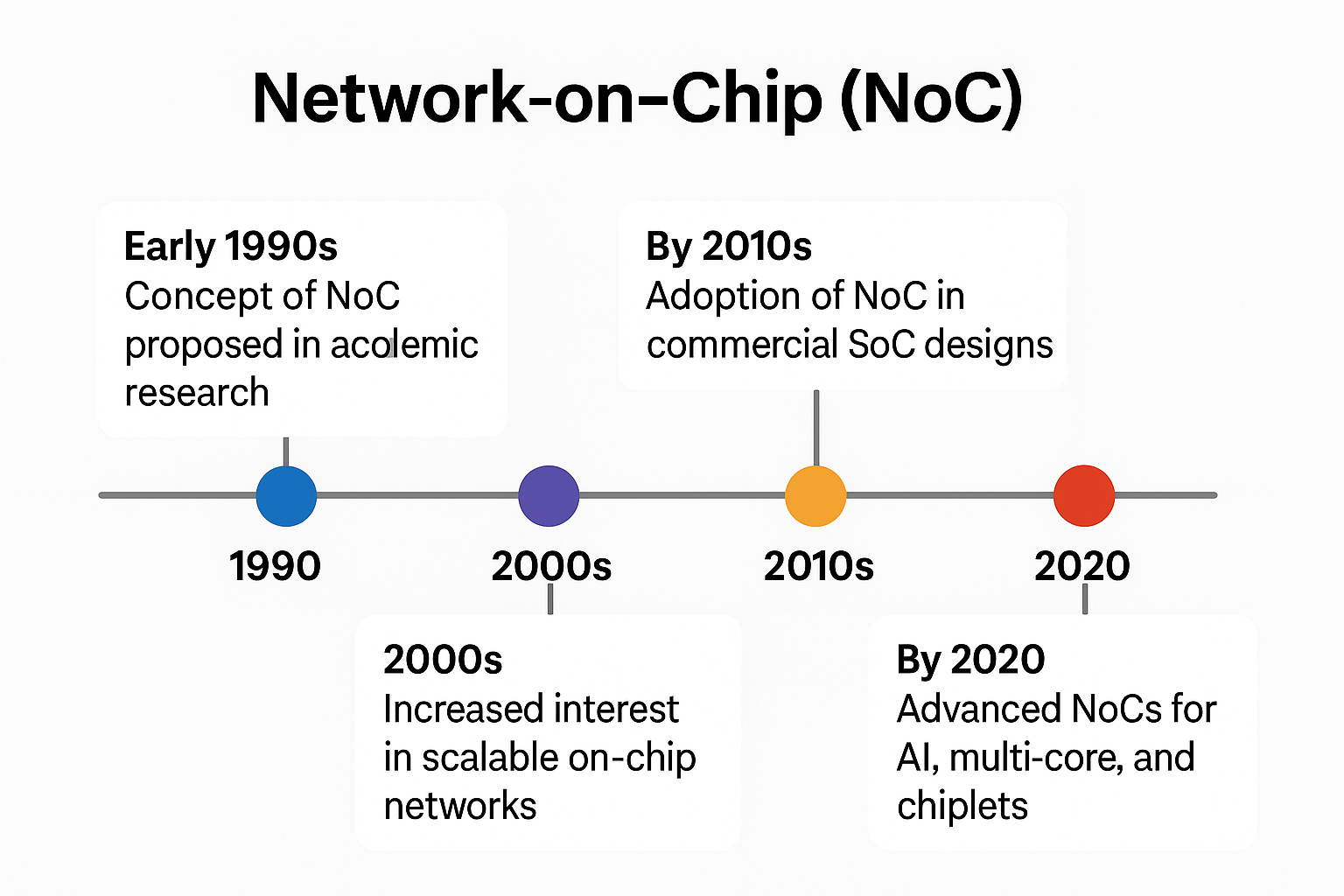

First Introduced: Early 2000s (concept); widespread in production ~2010+

Key Standards & Technologies: AMBA (Arm), CHI, TileLink, AXI NoC, proprietary fabrics

Overview

A Network-on-Chip (NoC) is a scalable communication infrastructure used to interconnect components within a System-on-Chip (SoC) or multiprocessor chip. NoCs replace traditional bus-based or point-to-point interconnects with a network-like structure composed of routers, links, and network interfaces, enabling efficient and parallel data transfers across cores, memory, accelerators, and I/O subsystems.

NoCs are critical to enabling multi-core, heterogeneous, and chiplet-based systems, where bandwidth, latency, power, and scalability are key concerns.

Why NoC?

Traditional Interconnect Challenges:

-

Shared bus bottlenecks with more cores

-

Poor scalability

-

Increased latency and congestion

-

High power and area costs for wide point-to-point links

NoC Benefits:

| Feature | Benefit |

|---|---|

| Scalability | Supports 10s to 100s of cores |

| Parallelism | Multiple simultaneous data transfers |

| Modularity | Decouples compute and communication |

| Efficiency | Optimized bandwidth, lower congestion |

| Configurability | Tailored topologies for specific workloads |

NoC Architecture Basics

1. Topology

Defines how routers and links are organized:

-

Mesh (most common in CPUs/SoCs)

-

Torus

-

Tree / Fat Tree

-

Ring

-

Crossbar

-

Hierarchical / Hybrid

2. Routing

Algorithms determine how packets move:

-

Deterministic (e.g., XY-routing)

-

Adaptive (responds to congestion)

-

Source routing (path chosen at injection)

3. Flow Control

Mechanisms to manage data traffic:

-

Wormhole routing (flit-level forwarding)

-

Virtual channels (prevent deadlock)

-

Credit-based / token-based systems

4. Switching Technique

-

Packet switching: Data in discrete packets

-

Circuit switching: Reserve path before transmission

-

Hybrid switching: Combines both

Components of a NoC

| Component | Role |

|---|---|

| Router/Switch | Directs data packets between NoC nodes |

| Link/Wire | Physical connection between routers or endpoints |

| Network Interface (NI) | Translates core/accelerator requests to network packets |

| Buffer | Temporarily stores data in routers |

| Arbiter | Resolves contention for shared resources |

Applications and Use Cases

1. Multi-core CPUs and GPUs

-

Intel, AMD, Apple, Arm, and NVIDIA chips use NoCs for connecting CPU/GPU clusters, caches, and memory controllers.

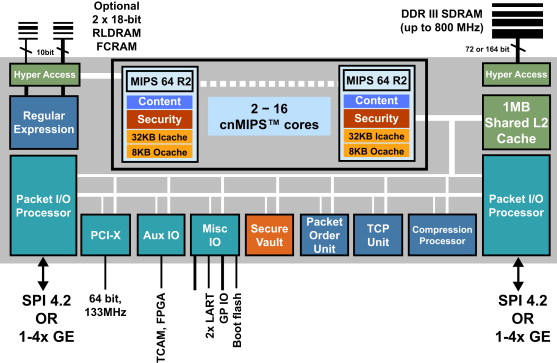

2. System-on-Chip (SoC)

-

Mobile SoCs (e.g., Qualcomm Snapdragon, Apple A-series) rely on NoCs to coordinate CPU, GPU, NPU, ISP, and DRAM.

3. AI Accelerators

-

AI chips (e.g., Google TPU, Cerebras WSE, Graphcore IPU) use advanced NoC topologies to connect hundreds or thousands of processing elements.

4. Chiplet Architectures

-

Inter-chip NoC-like fabrics (e.g., UCIe, AMD Infinity Fabric) allow chiplets to function as unified systems.

5. Heterogeneous Systems

-

Integrating CPU, GPU, DSP, NPU, and domain-specific cores with shared interconnect.

Key Commercial and Open NoC Implementations

| Provider/Type | NoC Technology |

|---|---|

| Arm | AMBA AXI, CHI Interconnect |

| Arteris IP | FlexNoC, Ncore (cache coherent) |

| NVIDIA | NVLink (chip-to-chip), mesh NoC in Grace |

| Intel | Tiled mesh NoC (Xeon), EMIB + Foveros |

| AMD | Infinity Fabric (multi-die interconnect) |

| Open-source | OpenPiton, OpenSoC, OpenNox |

| Academic | MIT RAW, Stanford SMART, Berkeley MWMR |

Design and Optimization Considerations

-

Latency vs. throughput trade-offs

-

Deadlock and livelock avoidance

-

Power-aware routing

-

QoS (Quality of Service) for real-time cores

-

Thermal-aware layout for dense 3D and chiplet designs

Advanced NoCs may also include:

-

Traffic monitoring and telemetry

-

Adaptive bandwidth allocation

-

Support for coherence protocols (e.g., MESIF, CHI)

Emerging NoC Technologies

| Innovation | Description |

|---|---|

| 3D NoC | Vertical interconnects in stacked dies (TSVs, hybrid bonding) |

| Photonic NoC | Uses light for communication to reduce latency and power |

| Wireless NoC | RF signaling for local wireless transfers in chip |

| Software-defined NoC | Programmable routing and QoS via firmware/hardware |

| AI-optimized NoC | Machine-learning trained traffic patterns and routing |

Challenges

-

Power consumption in high-frequency NoC routers

-

Verification complexity (deadlocks, protocol bugs)

-

Integration with legacy bus/IP interfaces

-

Latency variability in dynamic workloads

-

Debug and observability of internal traffic

NoC vs. Traditional Interconnect

| Feature | Traditional Bus | Point-to-Point | Network-on-Chip |

|---|---|---|---|

| Scalability | Poor | Moderate | Excellent |

| Latency | Low (small systems) | Moderate | Configurable |

| Bandwidth | Limited | Medium | High |

| Complexity | Simple | Medium | Complex |

| Flexibility | Low | Moderate | High |

Conclusion

Network-on-Chip (NoC) is a foundational technology for modern semiconductor design, enabling scalable, high-bandwidth, and efficient communication in increasingly complex chips. As SoCs grow more heterogeneous, and chiplet-based designs become standard, NoCs will evolve to support programmability, AI acceleration, and security, becoming the “nervous system” of next-generation compute platforms.

Share this post via:

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?