Tuesday morning at DAC I enjoyed a free breakfast courtesy of Synopsysand GLOBALFOUNDRIESwhere I learned more about the emerging market of IoT, and what it means to semiconductor, EDA and IP vendors. Panelists included: Semico Research, HP, Synopsys, GLOBALFOUNDRIES and Broadcom. Continue reading “IoT Breakfast Panel at DAC”

Ceaseless Field Test for Safety Critical Devices

While focus of the semiconductor industry has shifted to DACin this week and unfortunately I couldn’t attend due to some of my management exams, in my spare time I was browsing through some of the webpages of Cadenceto check their new offerings (although they have a great list of items to showcase at DAC) and to my pleasure I came across a really interesting, important one for this age of high-end SoCs which demand very high reliability. Considering the chips which need to withstand extreme temperature and other environmental conditions, their one-time testing is not sufficient. In case of applications such as automotive, they also need to bear with constant movement of a vehicle for its lifetime and hence need continued testing to be reliable. An in-built solution for testing such chips on their power-on for their lifetime is nothing less than a timely saviour of the system, equipment, vehicle and human life.

The solution for such a testing in Cadence Encounter Platform is the need of the hour. It’s a DFT methodology which can be used for on-board real world test; as soon as the system turns on, the chip can be tested and in case of any failure an error code can be generated to provide warning indication.

It’s LBIST (Logic Built-in Self-Test) function included in the chip along with a PRPG (Pseudo Random Pattern Generator) and a MISR (Multiple Input Shift Register). All scan elements are provided with known stimuli which are generated by the LBIST macro and are derived from a seed in the PRPG. The static and at-speed testing is done by capturing values and scanning them through the MISR. The MISR contains prior values which are compared with captured values and final MISR signatures are checked to verify the correct operation of the chip.

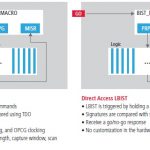

There are two different types of interfaces to LBIST in the Encounter Test LBISToption to Encounter RC (RTL Compiler). The Direct Access LBIST is easily executed by holding a pin high. The MISR signatures are compared with the stored internal values and a simple go/no-go response is provided to determine if LBIST has finished successfully. The smallest form factor for the Direct Access LBIST macro starts with 100 flip flops. This arrangement is simple and provides high quality results. The other interface, JTAG Access LBIST uses JTAG interface and protocols to start and execute LBIST. The signatures are compared off-chip in a higher level service processor or board-level devices. This arrangement allows customization of LBIST parameters in the silicon to run different testing scenarios. The smallest form factor starts from 160 flip flops. The LBIST macro area is increased to include shorter and more scan channels for increasing the speed of LBIST run.

In order to increase the test coverage, extra testpoints are optimally chosen and placed at suitable locations. This is automatically done by using RRFA (Random Resistance Fault Analysis) technique available in the Encounter Test DFT Architect as an add-on option to Encounter RC. The analysis can be done early in the design cycle to determine if testpoints are needed.

The Encounter RC cockpit provides a seamless environment for insertion and connection of the LBIST macro into the front-end design netlist and optimization of area, power, timing and test coverage through synthesis. The RTL Compiler also generates all downstream scripts to verify design equivalence with Cadence Conformal LEC, generate test patterns, signature, and fault coverage metrics with Encounter Test True Time ATPG, and MISR signature verification with Cadence Incisive ncverilog simulation.

From the safety standard perspective, the automotive industry has set standards such as ISO 26262 and AEC-Q100 which must be met by the hardware and software provided by electronics suppliers. The Cadence Encounter Test LBIST provides an ideal solution to meet these criteria, in-built into the chip and that can be tested throughout the product life cycle.

Although in general LBIST provides a low pin interface, the Direct Access LBIST interface is a unique solution for mixed-signal and pin-limited designs used in automotive applications. Dale Meehl at Cadence has described the overall methodology in a whitepaper posted at Cadence website. It’s an interesting read!

More Articles by Pawan Fangaria…..

lang: en_US

High Sigma Yield Analysis and Optimization at DAC

When I hear the phrase “high sigma” I think of the EDA vendor Solido, however at DAC on Monday I visited another EDA company called MunEDAthat has several products of interest to transistor-level IC designers. I was able to speak with three different people from MunEDA and here’s what I learned.

Continue reading “High Sigma Yield Analysis and Optimization at DAC”

AMS Panel: Micronas, Infineon, AMD, STMicro

Synopsyshosted an AMS Luncheon panel today at DACin the Westin Hotel and invited four customers to talk about their actual design challenges and experiences. I’ve typed up my notes from this event.

Continue reading “AMS Panel: Micronas, Infineon, AMD, STMicro”

Affordable AMS EDA Tools at DAC

First thing at DACtoday I met with Greg Lebsack of Tanner EDA to ask about what’s new in the past year for his EDA company. Here are my meeting notes, so there’s not much prose for my DAC blogs this year.

Continue reading “Affordable AMS EDA Tools at DAC”

Getting the best from a Radio Spectrum: MIMO

Exchanging data through wireless network is that we are doing every day, every hour if not every minute. Not only we use our smartphone to discuss or exchange Emails, but also to download, or upload, massive amounts of data. Thus, the radio spectrum has become to be busy, and is an expansive piece for carriers. Optimizing this radio spectrum is both a technical and business requirement! Just read this white paper from CEVA to better understand MIMO.

One Digital Signal Processing based technique is gaining strong traction, Multiple Input Multiple Output (MIMO). MIMO is just like magic, as it could allow a x4 bandwidth multiplication, both for emission and reception. This DSP technique is all but trivial, but with good DSP engineer developing the right algorithm on the right piece of hardware, here a DSP core from CEVA, it’s possible to boost a base station and reach such bandwidth multiplication.

I could try to explain Antenna Correlation (above) or MIMO 4 level tree with QPSK Modulation (below), but I would not be as didactic as Noam Dvoretzki and Zeev Kaplan from CEVA, so I recommend you to read this white paper “MIMO Maximum Likelihood Detector” posted here, on CEVA web site.

In the conclusion, the white paper states that MLD receiver achieves superior results to the linear receiver, and describes the factors that need to be considered when choosing an MLD implementation. Choosing an optimized MLD receiver can be the main differentiator in a cellular product!

Eric Esteve from IPNEST –

More Articles by Eric Esteve…..

lang: en_US

Advice for Out-of-towners

You are visiting San Francisco and you have dutifully read your guide book. Let me give you some contrarian advice.

See the Golden Gate Bridge. The best way is not to drive there or get a taxi, but to rent a bicycle (lots of places on that side of the city, try Googling “blazing saddles”) and cycle across the bridge. You can then go down the hill into Sausalito. There is a regular ferry back from Sausalito to San Francisco and you can take your bike on it. Or you can keep going to Tiburon, almost flat, and get the ferry back from there.

Take a Tour of the Bay but ignore the official tours of the bay. Just take the ferry to Sausalito (from the Ferry Building or from pier 41), have a drink or a bite to eat, and get the ferry back. Cheapest bay tour available and voted the #2 most exciting ferry ride in the world by the Association of American Travel Writers (Kowloon to Hong Kong is #1 so rather a long way to go, and having done it, I don’t think it is even as good).

Ride a Cable Car. But don’t wait in line for 40 minutes at Union Square or Fisherman’s Wharf. Instead, go to the cable car barn on the corner of Washington and Mason. This where the whole system is driven from and you can watch the engines hauling the miles of cable under the streets. Also a museum of everything cable car. And then when you have finished, you can just get on a cable car without needing to stand in line, and go back downtown or to fisherman’s wharf. The best ride is not to sit but to stand on the outside and hang on. Especially around the corners…slightly scary.

Don’t go to Fisherman’s WharfandPier 39. Everybody who lives here will tell you it’s not worth it. OK, so you are going to go anyway. Then at least go and see the Musée Méchanique on Pier 45. It is a huge selection of coin-operated antique arcade machines. It is free although you’ll presumably spend at least a few quarters in the machines.

See Chinatown. Here’s the best way to do it. Go to Union Square. Go shopping if that’s your thing. Then leave Union Square on Stockton Street and walk through the Stockton Street Tunnel. When you come out at the other end you are in the back of Chinatown and it is like you have landed in another country. Stockton Street is the non-touristy part of Chinatown, full of food shops and the like. Go down the hill one block to Grant Street if you feel the need to buy the sort of things tourists like to buy in Chinatown.

Go to Alcatraz. Warning: you must book a few days in advance. You will not get tickets if you just show up. Really. It is June. I’m publishing this far too late, you probably can’t get tickets within a week. Much the best is to take the night tour, which leaves around 6 and gets back around 9. There are fewer people on the island and you get to watch the sun set through the Golden Gate. The ferry leaves from pier 33. You can buy tickets online.

The Exploratorium is the original hands-on science museum. It has moved if you visited it before. It is now on the waterfront at pier 15 in brand-new multi-million dollar accommodations. Local donors are very generous. It is even more amazing than it used to be.

Finally a few shops with some history:

- City Lights Books founded in 1953 and closely associated with Allen Ginsburg and the other beat poets. A publisher as well as a bookstore, and now an official historic landmark. 261 Columbus at Broadway. Website.

- 826 Valencia, the Pirate Store. It is actually a place for helping kids 6-18 with their writing skills, but they were in a space zoned for retail so they had to be a store too. They decided to be a pirate supply store. And they are. The story is told in this TED video. They have websites: Writing, Pirates. If you want a T-shirt that says “Cannons don’t sink ships, Pirates with cannons sink ships” then this is the place to visit.

- Good Vibrations, female friendly sex-shop since 1977. One block from Moscone, 899 Mission Street at 5[SUP]th[/SUP] and 2 other places in the city. And a website. Totally unembarrassing to visit even if you are shy. I’m a guy, sure, but trust me. I’ve taken reluctant asian girls who loved it..

- Ferry Building Farmers’ Market. On Saturday mornings, so you probably missed it. The quality and range of the produce is extraordinary but you won’t save any money, even compared to Whole Foods. Go early if you want to have fun trying to spot celebrity chefs. In the parking lots around the Ferry Building where Market Street ends at the bay.

Gary Smith at DAC

Gary Smith once again wore his signature white coat and extolled the virtues of system level design and automation. The room at the Intercontinental was packed, and the folks in the hallway outside were noisy as usual, eager for the party to start after Gary finished.

Everything You Wanted to Know About the Internet But Were Afraid to Ask

Every year, Mary Meeker produces a huge presentation (140 slides) on important trends in the internet. This year’s came out at the end of last week. It is well worth the time it takes to go through it. Here is the first slide, effectively the table of contents:

- Key Internet Trends

- Status Update: Tech Stocks / Education / Healthcare

- Re-Imagining Continues

- Screen + Video Growth = Still Early Innings

- China’s Epic Share Gains

- Public Company Trends

- One More Thing(s)…

- Ran Outta Time Thoughts / AppendixI am going to pick out a few slides to whet your appetite.

First let’s look at how fast tablets are growing compared to the historical growth of the PC market. They have already passed PCs in numbers and are still selling at an amazing pace, the line is close to vertical.

Next, the OS used in smartphones. Eight years ago they were all foreign (Blackberry from Canada, and Symbian from Finland primarily). Now the US has 97% market share between iOS, Android and WindowsPhone.

Finally, how international is the internet? Probably a lot more than you think. 86% of users are overseas, even for people like Google and Facebook never mind the big China-based internet companies like Baidu and Tencent.

Apple is Roaring Back!

Mind you, this post is being written by the same guy who wrote8 Reasons Why I Hate My iPhone 5. I’ve been living with the Samsung S4 for about a year, and am ready to return to the Apple fold. It’s partially that too many, or perhaps the wrong apps running on my phone cause big problems. This manifests itself anywhere from people receiving my calls hearing a modem buzz, to Google Maps and the GPS getting confused every time I use my hiking app. Needless to say I am a frequent rebooter.

I watch Apple very closely as I own some stock. I believe the company has hit and inflection point. When Apple’s Eddy Cue touts ‘best product pipeline’ in 25 years , I buy it. I’m also influenced by the fact that my techie son, at Stanford, has gone from an Apple hater, to an Apple lover. He is so impressed with his MacBook Air that he will be upgrading from his S3, which he doesn’t like much, to the iPhone 6.

I digress. The reasons I believe the Apple will come roaring back, are:

[LIST=1]

Let’s hope the stock hits $100/share, post 7:1 split, in the very near future, then roars upward from there!

lang: en_US