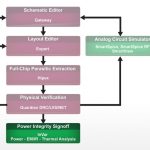

NetSpeed has developed NocStudio, a front end optimization design tool helping architects to create SoC architecture bridging the gap with the back end, floor planning and place and route. At the chip level, NocStudio generates a cache-coherent Network-on-Chip (NoC) allowing interconnecting the various CPU, GPU or Acceleration engines (the Cache-Coherent Clusters) with the I/O-Coherent and Noncoherent Agents by the means of Multiple Cache-Coherent Controllers. NetSpeed Gemini coherent NoC is high performance, scalable, and highly configurable for a wide range of applications and provides multiple benefits like routing and channels optimization, much easier place & route and lower power consumption.

But coherency is all about sharing and there is a complex set of protocols to make sure that sharing happens correctly. A bug in any part of the execution can bring down the complete scheme and product. In that sense, NetSpeed’s Gemini NoC is also an additional IP function which needs to be extensively verified. Let’s see how NetSpeed has addressed the verification challenges linked with this highly configurable coherency IP.

The first challenge is linked with the very specific IP nature: for a cache-coherent NoC, the verification space state is massive. Such a NoC is created to avoid deadlocks, fatal and unrecoverable errors, but also rare events requiring large warm-up periods, as bugs manifest after millions of cycles. Running millions of cycles at simulation level translate into weeks, so NetSpeed decided to use the Cadence® Palladium XP acceleration/emulation platform as part of its multi-layered approach to exhaustively verify Gemini NoC IP. The initial implementation and bring up phase takes about one week and this investment generate a quick return as NetSpeed could run in minutes on the emulation platform simulations cases taking one to two weeks on a simulator.

The next challenge comes from the very high configurability of the cache-coherent NoC IP. All these parameters can vary:

- Number of masters (from 1 to 64)

- Number of slaves (up to 200 I/O coherent and non-coherent agents)

- Topology

- Performance and power requirements (PPA)

- Quality of Service (QoS) levels

NetSpeed has developed NocWeaver as a systemic solution to address large state space verification. NocWeaver, integrated into NocStudio design flow, is a random NoC generator, able to generate 1000 configurations per night.

NetSpeed decided on a “depth and breadth” verification strategy that used simulation to quickly cover large numbers of configuration and emulation to validate complex time-dependent scenarios.

The next challenge is the need for intelligent coordinated stimulus. The goal is to run realistic coherency testing, to identify false sharing, true sharing and trust zone when coordinated coherency tests will check for index trashing, credit control and delay randomization. Thanks to self-checking stimulus, error detection will be made on a timely manner.

To summarize, emulation with Palladium allows to quickly running hundreds of NoC configurations and easy detection of errors. Because the NoC verification has been built to be deterministic, a bug detected in emulation can be reproducible in simulation and debug is done in simulation, using additional checkers.

The main challenge with highly configurable, flexible and scalable NoC IP is the verification time. NetSpeed has used several techniques to minimize this run time. Cache initialization sequences are different in simulation (caches states are pre-loaded) and emulation where initialization is done with real HW states machines. As well the reset sequences are done by using backdoor in simulation when emulation runs full reset sequences. Finally, exit checks, expensive to verify every time in simulation can be run much faster in emulation.

Cache-coherent NoC IP verification induces multiple challenges (massive state space, large warm-up period, reproducibility, etc.), associated with business challenges to deliver the product on time and being able to build customer confidence in a new and complex IP. Even if taking highly configurable and complex IP like for example PCIe 4.0 protocol, NoC verification add one level of challenge: every SoC is different and keep the product specification “open”, when compared with any protocol specification.

NetSpeed has built a complete verification strategy, based on “depth and breadth”, using emulation to run very fast verification of hundreds of configurations, detect bugs and reproduce it in simulation to easy debug the IP. That’s a high price paid by NetSpeed to release a trustable cache-coherent NoC IP in the field.

From Eric Esteve from IPNEST