– First SEMICON in Arizona was great- should make it permanent

– Congress finally wakes up to China issues long after cows are gone

– Memory cycle in support of AI could be huge but scary at same time

– AI demand seems bottomless- but may distort chip industry dynamics

Phoenix SEMICON was wonderful!

The crowds and attendance were huge . Lots of good displays and a very energized crowd. The aisles were packed the first two days and calmed down on the third and final day.

The vibe was definitely better than the more recent SEMICON West shows held in San Francisco. It just felt better and more upbeat and not just because of the happy atmosphere in the industry but just overall nicer (maybe it was the weather)

We think that the move to Phoenix should be made permanent as it is certainly much more relevant when you are a short drive from both TSMC and Intel fabs.

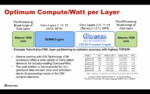

Applied Materials kicks off first day of SEMICON with new products

Applied used the conference to announce three new products that all seem to be strong contenders.

The “Kinex” die to wafer bonding system which is critical to new packaging applications.

The “Xtera” EPI (epitaxial) system for void free epitaxial deposition, which harkens back to AMATs start in the industry decades ago with its first product being an EPI systems.

The third announcement was the PROVision E-Beam system which is clearly needed as the the industry gets down to low nanometer sized features.

We would point out the real winner behind the scenes is BESI , who are the real force behind the Kinex die to wafer bonding tool that AMAT is white labeling as their own. BESI gets the benefit of AMAT’s huge size pushing their product for them. But both companies obviously win.

We would also point out that the die to wafer bonding market is getting very crowded as we count at least 8 makers of similar technology. We would anticipate aggressive pricing in this area which is critical to multi-chip packaging.

Damning congressional report seems timed for maximum effect

We have been talking about the risks of selling China semiconductor equipment for over a decade now, far longer than any other analyst.

Congress is certainly way late to the game as the cows are long gone from the unlocked barn…but it is somewhat better late than never.

The report is quite damning as it chronicles what we have long known about the equipment industry profiting from the sales of tools that help the Chinese military against ourselves. As we have repeated “selling them the rope to hang us with” (Vladimir Lenin)

Selling the Forges of the future

Its well worth reading the entire above report…..

It mentions the top 5 players; AMAT, LRCX, KLAC, ASML and TEL

We think its going to be more difficult for the equipment players to up their tens of millions of dollars spent on K street lobbying firms in Washington DC to spread wealth around DC to keep export restrictions at bay. The report is direct , bi-partisan and hard to ignore and could prove embarrassing in a critical upcoming election cycle.

We have talked for many years about simply restricting any 300MM equipment from being exported to China. Anything short of that will have loopholes and work arounds and ways to skirt restrictions. All you need is a tape measure that can read 8 or 12 inches. It was somewhat interesting to see the congressional report finally talking about 300MM restrictions.

They obviously creates a further downside bias on sales to China which were already coming down. We would anticipate that we could see further downside revisions especially if current loopholes get closed. We think the majority of the negative impact will be on the named top 5 players. Second tier and smaller players will likely escape much of the scrutiny.

We also anticipate that China will try to slow their buying from the top 5 as they could get stuck with million dollar paperweights without service and spare parts.

We could be seeing the beginning of a super strong memory cycle driven by AI demand

We know very well what AI chip demand has done to the foundry business. A similar benefit is obviously underway on the memory side as well.

The recent 900K wafer starts/month deal between SK and OpenAI is beyond huge. Even if its only half that number its still huge…

We could see unprecedented ramp of memory capacity with the primary limiting factor being factory floor space.

AI is obviously memory hungry and a limiting factor.

While this could be great for the next couple of years as prices will remain high and equipment sales will be great the hangover after the party could also be devastating.

However, that’s too far in the future to care about now and the stocks won’t care either.

The stocks

The stocks have been on fire for quite some time and will likely need some cooling off and pull backs here and there as they are just so overheated.

Fighting the tape and positive news flow is pointless here.

We see no reason to sell or worse take a short position as you will only get crushed by the positive news.

Its best to just go along for the ride which seems to be quite thrilling right now.

We are still at the beginning of what could be one of the best up cycles the industry has ever seen. The upcycles just keep getting bigger and better……

PCs, the internet, mobile phones, now AI…..what’s next??? Quantum??? Maybe I’ll be retired by then……

About Semiconductor Advisors LLC

Semiconductor Advisors is an RIA (a Registered Investment Advisor),

specializing in technology companies with particular emphasis on semiconductor and semiconductor equipment companies.

We have been covering the space longer and been involved with more transactions than any other financial professional in the space.

We provide research, consulting and advisory services on strategic and financial matters to both industry participants as well as investors.

We offer expert, intelligent, balanced research and advice. Our opinions are very direct and honest and offer an unbiased view as compared to other sources.

Also Read:

AMAT China Collapse and TSMC Timing Trimming

Is a Semiconductor Equipment Pause Coming?

Musk’s new job as Samsung Fab Manager – Can he disrupt chip making? Intel outside