These are stressful times in functional verification. We are being pushed to more aggressively embrace AI-based automation, knowing we will continue to be held accountable for quality of results. Verification misses could upend careers, maybe enterprises. It is tempting to believe that sanity will prevail and we will ultimately… Read More

Tag: verification

Axiomise Introduces nocProve to Transform NoC Design Verification

Axiomise has recently launched a new verification tool called nocProve which will transform how Network-on-Chip designs are validated in modern hardware development, absolutely.

The tool is designed to be the first configurable formal verification application specifically created for NoC implementations. It addresses… Read More

Verification Futures Conference 2026 UK

Verification Futures UK 2026, co-located with Semiconductors Futures 2026 organised by Tessolve and co-organised this year with Alpinum. The conference continues its strong tradition of delivering a unique blend of conference presentations, exhibitions, training, and industry networking sessions focused on the challenges… Read More

Webinar: Why AI-Assisted Security Verification For Chip Design is So Important

In this webinar, we will explore the growing threat that AI-fueled cyberattacks pose to chip designs and how to add expert-level security verification to your design flow to minimize those risks.

We will expose some of the details of the existential risk for electronic systems with real examples. We will then describe technology… Read More

Transforming Functional Verification through Intelligence

SoC projects are running behind schedule as design and verification complexity has increased dramatically, so just adding more engineers, more tests and more compute aren’t the answer. The time is ripe to consider smarter ways to improve verification efficiency. The added complexity of multiple embedded processors, multiple… Read More

Agentic Bug Localization. Innovation in Verification

Bug localization continues to be a challenge for both bug triage and root-cause analysis. Agentic approaches suggest a way forward. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and lecturer at Stanford, EE292A) and I continue our series on research ideas.… Read More

DVCON U.S. 2026

DVCon is the premier conference on the application of languages, tools, and methodologies for the design and verification of electronic systems and integrated circuits. The focus of the conference is the usage of specialized design and verification languages such as SystemVerilog, Verilog, VHDL, PSS, SystemC and e, as well… Read More

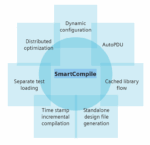

Revolutionizing Simulation Turnaround: How Siemens’ SmartCompile Transforms SoC Verification

In the race to deliver ever-larger SoCs under shrinking schedules, simulation is becoming a bottleneck. With debug cycles constrained by long iteration times—even for minor code changes—teams are finding traditional flows too rigid and slow. The problem is further magnified in continuous integration and continuous deployment… Read More

AlphaDesign AI Experts Wade into Design and Verification

I mentioned in an earlier blog that multiple presentations at DVCon 2025 went all-in on AI-assisted design and verification. The presentation was one such example, looking very much at top-down AI-expert application of agentic flows to design and verification. AlphaDesign is a new startup out of UC Santa Barbara headed by William… Read More

Automating Reset Domain Crossing (RDC) Verification with Advanced Data Analytics

The complexity of System-on-Chip (SoC) designs continues to rise at an accelerated rate, with design complexity doubling approximately every two years. This increasing complexity makes verification a more difficult and time-consuming task for design engineers. Among the key verification challenges is managing reset domain… Read More