There is an old saying popularized by Mark Twain that goes “There are three kinds of lies: lies, damned lies, and statistics.” It turns out that no one can say who originated this saying, yet despite however you might feel about statistics, they play an important role in verifying analog designs. The truth is that there are large numbers… Read More

Tag: variation

Free Webinar: Analog Verification with Monte Carlo, PVT Corners and Worst-Case Analysis

The letters “PVT” roll of the tongue easily enough, belying the complexity that variations in process, temperature and voltage can cause for analog designs. For semiconductor processes, there are dozens of parameters that can affect the viability of a design. It would be easy enough to optimize a circuit with only one or two varying… Read More

Free Webinar on Standard Cell Statistical Characterization

Variation analysis continues to be increasingly important as process technology moves to more advanced nodes. It comes as no surprise that tool development in this area has been vigorous and aggressive. New higher reliability IC applications, larger memory sizes and much higher production volumes require sophisticated yield… Read More

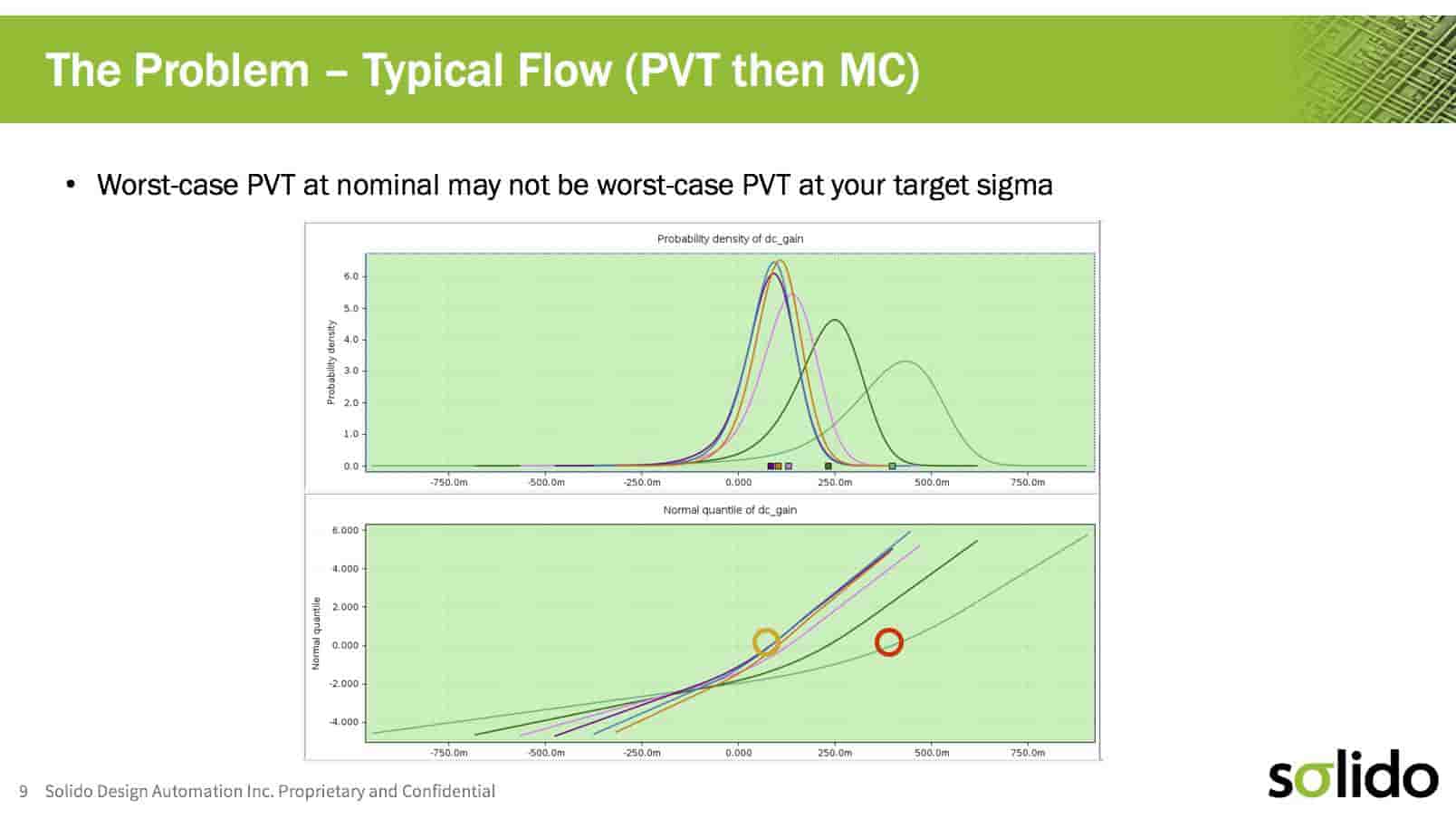

A better way to combine PVT and Monte Carlo to improve yield

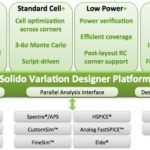

TSMC held its Open Innovation Platform Forum the other week on September 13[SUP]th[/SUP]. Each year the companies that exhibit at this event choose to highlight their latest technology. One of the most interesting presentations that I received during the event was from Solido. In recent years they have produced a number of groundbreaking… Read More

We Need Libraries – Lots of Libraries

It was inevitable that machine learning (ML) would come to EDA. In fact, it has already been here a while in Solido’s variation tools. Now it has found an even more compelling application – library characterization. Just as ML has radically transformed other computational arenas; it looks like it will be extremely disruptive here… Read More

Webinar Offers View into TSMC IP Design Methodology

Standard cell and memory IP are key enablers for new process node availability. These two items must be in place early and be completely ready for a process node to scale to volume. Development of both leaves no room for error and they require the highest performance possible. Foundries are extremely focused on this and spend a lot… Read More

TSMC and Solido to Share Experiences with Managing Variation in Webinar

TSMC knows better than anyone the effect that variation can have at advanced process nodes. Particularly in memory designs and in standard cell designs, variation has become a very critical because of its effects on yield and because of the high-cost of compensating for it. Smaller feature sizes combined with lower voltage thresholds… Read More

Statistical Simulation Provides Insight into 6T SRAM Optimization

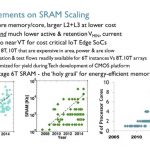

ARM’s Azeez Bhavnagarwala recently gave a talk hosted by Solido on the benefits of variation aware design in optimizing 6T bit cells. Azeez sees higher clock rates, increasing usage of SRAM per processor and the escalating number of processors, shown in the diagram below, as trends that push designers toward 6T. Six Transistor… Read More

How TSMC Tackles Variation at Advanced Nodes

The design community is always hungry for high-performance, low-power, and low-cost devices. There is emergence of FinFET and FDSOI technologies at ultra-low process nodes to provide high-performance and low-power requirements at lower die-size. However, these advanced process nodes are prone to new sources of variation.… Read More

Moving with Purpose for Certainty

In 1492 Christopher Columbus sailed from Spain towards west on Atlantic Ocean in search of Asia and Indies. Between his four voyages (1492 – 1502) he discovered many different islands and then what we call Americas. Although he had a compass with him, imagine searching a needle in a haystack. Even with localization of areas and then… Read More