You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Accellera invited me to attend their #61DAC panel discussion about the new Portable Stimulus Standard (PSS) v3.0, and the formal press release was also just announced. The big idea with PSS is to enable seamless reuse of stimulus across simulation, emulation and post-silicon debug and prototyping.

Tom Fitzpatrick from Siemens… Read More

Transistor-level circuit designers have long used SPICE for circuit simulation, mostly because it is silicon accurate and helps them to predict the function, timing, power, waveforms, slopes and delays in a cell before fabrication. RTL designers use digital simulators that have a huge capacity but are lacking analog modeling.… Read More

Dr. Nasib Naser brings over 35 years of experience in the field. His expertise spans the entire VLSI cycle from conception to chip design, with a strong focus on verification methodologies. For his 17 years at Synopsys, Dr. Naser have held senior management positions, leading North American Verification IP, managing Central … Read More

Axiomise pioneered the adoption of formal verification in the semiconductor industry since 2017. Led by visionary CEO, Dr. Ashish Darbari, who has 63 patents in formal verification, and Neil Dunlop an industry veteran with 40 years of experience, Axiomise has helped twenty customers over the last six years by providing them… Read More

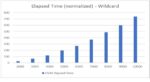

The Universal Verification Methodology (UVM) is a popular way to help verify SystemVerilog designs, and it includes a configuration system that unfortunately has some speed and usage issues. Rich Edelman from Siemens EDA wrote a detailed 20-page paper on the topic of how to avoid these issues, and I’ve gone through it to… Read More

When I first heard the term ‘bespoke silicon,’ I had to get my dictionary out. Well versed in the silicon domain, I did not know what bespoke meant. It turns out to be a rather old-fashioned term for tailor made and seems to be very much British English. The word dates from 1583 and is the past participle of bespeak, according… Read More

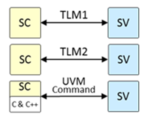

Siemens EDA is clearly on a mission to help verifiers get more out of their tools and methodologies. Recently they published a white paper on UVM polymorphism. Now they have followed with a paper on using UVM Connect, re-introducing how to connect between SystemC and SystemVerilog. I’m often mystified by seemingly overlapping… Read More

Rich Edelman of Siemens EDA recently released a paper on this topic. I’ve known Rich since our days together back in National Semi. And I’ve always been impressed by his ability to make a complex topic more understandable to us lesser mortals. He tackles a tough one in this paper – a complex concept (polymorphism) in a complex domain… Read More

Sometimes we miss the forest for the trees, and I’m as guilty as anyone else. When we think testbenches, we rightly turn to UVM because that’s the agreed standard, and everyone has been investing their energy in learning UVM. UVM is fine, so why do we need to talk about anything different? That’s the forest and trees thing. We don’t … Read More

In my last blog post about AMIQ EDA, I talked with CEO and co-founder Cristian Amitroaie about their support for continuous integration (CI). We discussed in some detail how their Design and Verification Tools (DVT) Eclipse Integrated Development Environment (IDE) and Verissimo SystemVerilog Linter are used in CI flows. Cristian… Read More