Multi-die design has become the center of a lot of conversation lately. The ability to integrate multiple heterogeneous devices into a single package has changed the semiconductor landscape, permanently. This technology has opened a path for continued Moore’s Law scaling at the system level. What comes next will truly be exciting.… Read More

Tag: UCIe PHY

AI System Connectivity for UCIe and Chiplet Interfaces Demand Escalating Bandwidth Needs

Artificial Intelligence (AI) continues to revolutionize industries, from healthcare and finance to automotive and manufacturing. AI applications, such as machine learning, deep learning, and neural networks, rely on vast amounts of data for training, inference, and decision-making processes. As AI algorithms become … Read More

Synopsys – TSMC Collaboration Unleashes Innovation for TSMC OIP Ecosystem

As the focal point of the TSMC OIP ecosystem, TSMC has been driving important initiatives over the last few years to bring multi-die systems to the mainstream. As the world is moving quickly toward Generative AI technology and AI-based systems, multi-die and chiplet-based implementations are becoming essential. TSMC recently… Read More

Disaggregated Systems: Enabling Computing with UCIe Interconnect and Chiplets-Based Design

The world of computing is evolving rapidly, with a constant demand for more powerful and efficient systems. Generative AI has driven exponential growth in the amount of data that is generated and processed at very high data speeds and very low latencies. Traditionally, computing systems have been built using monolithic designs,… Read More

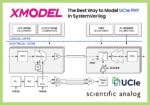

WEBINAR: UCIe PHY Modeling and Simulation with XMODEL

Join this webinar and see UCIe in action! This webinar presents the SystemVerilog models of a Universal Chiplet Interconnect Express (UCIe) interface, including both the analog circuits in the electrical layer and digital FSMs in the logical layer. The whole physical layer (PHY) model can be efficiently simulated in SystemVerilog,… Read More