This week, I had a nice opportunity meeting Charu Puri, Corporate Marketing and Sushil Gupta, V.P. & Managing Director at Atrenta, Noida. Well, I know Sushil since 1990s; in fact, he was my manager at one point of time during my job earlier than Cadence. He leads this large R&D development centre, consisting about 200 people… Read More

Tag: tsmc

TSMC Q2 Results: Up 17%; 20nm and 16nm on track

TSMC announced their Q2 financial results yesterday. Revenue was $5.2B (at the high end of guidance) with net income of $1.6B. This is up 17.4% on Q1 and up 21.6% year-to-year. Gross margin is up too, at 49% which is up 3.2 points on Q1 and 0.3 points year-to-year. As usual the financial results are not directly that interesting since… Read More

The Semiconductor IDM Business Model is Dead!

While this was not specifically stated, it was certainly implied during the sessions I attended at SEMICON West this week: The traditional semiconductor business model (IDM) is coming to an end. Starting with the keynote: Foundry-driven Innovation in the Mobility Era,cost was the common theme in any discussion involving mobile… Read More

The Future of Mobile Semiconductor Devices

During my trip to Taiwan I hopped on over to Hong Kong for a speaking engagement. One of the things I do as an “Internationally Recognized Industry Expert” is help the financial world understand the semiconductor landscape as it pertains to SoCs and mobile devices. Usually I do this over the phone or in writing but I prefer to do it in… Read More

What is inside the iPhone5s? Samsung or TSMC?

As a semiconductor professional and an Apple customer I’m very interested to see what is inside the iPhone5s. Rumors are spreading, photos are leaking, creating a nice build up to the next release of the mobile device that changed the world.

Honestly, last year I was a bit disappointed with the iPhone5. Inside is the A6 SoC which uses… Read More

TSMC and Xilinx on the FinFAST Track!

The power of the fabless semiconductor ecosystem never ceases to amaze me. On one hand you have the Intel backed press crowing about Intel stealing Altera from TSMC. On the other hand you have Xilinx and TSMC crowing about a new ‘one-team’ approach. If you are interested in the real story you’ve come to the right place.

“Altera’s… Read More

Taiwan Semiconductor Tries To Pull A FinFAST One!

This completely misleading title is from a Seeking Alpha (SA) article, a stock investment version of the National Enquirer. As I mentioned inA Call to ARMs, fame and fortune seeking SA Authors make a penny per click so sensationalism sells. The article is not worth your time so I will save you the click and skip to the misguided conclusion:… Read More

A Call to ARMs!

It sure has been an interesting experience watching Intel enter the semiconductor foundry business! While I credit Intel for increasing the exposure of the fabless semiconductor ecosystem to the financial markets, the attention from the Intel biased press is a bit overwhelming. The TSMC and ARM bashing is reaching new levels… Read More

Meeting with Sidense at TSMC Technology Symposium

If you have attended DAC in Austin (June 2-5), you probably have missed the first TSMC Technology Symposium. It was held on June 6 in Shanghai. Considering my own experience of a 29 hours trip to come back home (in France), I doubt that it was any possible to leave Austin on June 5 to attend TSMC Technology Symposium in Shanghai on June… Read More

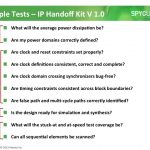

DAC IP Workshop: Are You Ready For Quality Control?

On Sunday I attended an IP workshop which was presented by TSMC, Atrenta, Sonics and IPextreme. It turns out that the leitmotiv of the afternoon was SpyGlass.

Dan Kochpatcharin of TSMC was first up and gave a little bit of history of the company. They built up their capacity over the years, as I’ve written about before, and last… Read More