Visiting a new EDA vendor at #61DAC is always a treat, because much innovation comes from the start-up companies, instead of the established big four EDA companies. I met with Vincent Bligny, Founder and CEO of Aniah on Wednesday in their booth, to hear about what they are doing differently in EDA. Mr. Bligny has a background working… Read More

Tag: transistor-level

Transistor-Level Static Checking for Better Performance and Reliability

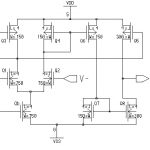

My first transistor-level IC design job was with Intel, doing DRAM designs by shrinking the layout to a smaller process node, and it also required running lots of SPICE runs with manually extracted parasitics to verify that everything was operating OK, meeting the access time specifications and power requirements across PVT … Read More

12 Reasons to Attend this Annual User Group Meeting for Transistor-level IC Designers

My first job out of college was transistor-level circuit design of DRAMs at Intel, so I’ve continued to be fascinated with both the craft and science of designing, optimizing, verifying and debugging custom ICs. Last October I traveled to Munich, Germany to attend a two day user group meeting for engineers using tools from… Read More

Transistor-Level IC Design is Alive and Thriving

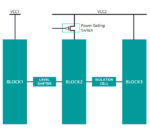

There’s much talk in EDA about High Level Synthesis (HLS), Transaction Level Modeling (TLM) and the Universal Verification Methodology (UVM), however there’s a lower-level of abstraction, the transistor-level, where high-speed digital cell libraries are created, analog circuits are crafted, and AMS designers… Read More

Transistor, Gate and RTL Debug Update at DAC

Debugging an IC design at the transistor, Gate and RTL levels is often necessary to meet timing requirements and understand analog or digital behavior, yet the process itself can be a tedious one, filled with manual steps, therefore making it an error-prone process. EDA tools have been created to help us graphically debug transistor,… Read More