You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Training Day at DACby Paul McLellan on 05-07-2013 at 12:15 pmCategories: EDA, Events

This year for the first time the Thursday of DAC is tranining day. So that would be June 6th in Austin, of course. There are four tracks of training focused on SystemC, ARM Cortex and two on SystemVerilog, all areas of increasing use in SoC design, especially in mobile.

Each track of training is divided into two parts, one held from 9am… Read More

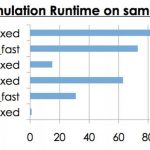

Often a question is raised about how SystemC improves verification time when the design has to go through RTL in any case. A simple answer is that with SystemC, designs can be described at a higher level of abstraction and then automatically synthesized to RTL. When the hands-on design and verification activity is at a higher level,… Read More

Unless you are a small company with one design team, the chance you have standardized on one FPGA vendor for all your needs, forever and ever, is unlikely. No doubt you probably have a favorite, because of the specific class of part you use most often or the tool you are most familiar with, but I’d bet you use more than one FPGA vendor routinely.… Read More

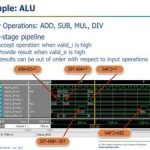

Many advanced algorithmic IPs are described in C++. We use this language because of its flexibility. Of course software algorithms are written to be executed on processors so they don’t solve all the issues of getting the algorithm implemented in hardware directly. This is not simply a high-level synthesis (HLS) issue. Usually… Read More

Promoted by Accellera, SystemC User Groups are in work worldwide; NASCUGin North America, ESCUGin Europe and ISCUG in India. While I was shuffling between my day-to-day work and strategy management course/exams, I received an invitation from my long time colleague, President and CEO of Circuitsutra Technologies, Mr. Umesh… Read More

Tom Feist of Xilinx presented here at the GlobalPress Electronics Summit about their strategy to take design abstraction up another level. In the SoC world, we are still pretty much stuck at the RTL level and have moved to higher abstractions by using an IP strategy. But at least all IC designers are RTL-literate.

Xilinx, in the Vivado… Read More

Mentor Shines at DVConby Beth Martin on 02-18-2013 at 12:30 amCategories: EDA, Siemens EDA

Mentor Graphics will be all over DVCon next week (February 25-28) at the DoubleTree hotel in San Jose.

In addition to attending all the panels, tutorials, posters, and the keynote, you can visit Mentor in booth 901 on the exhibit floor.

Here’s the lineup of Mentor-related events:… Read More

One of the decisions that needs to be made when using high-level synthesis (HLS) in general and Catapult in particular is what language to use as input. The choice is C++ or SystemC. Of course at some level SystemC is C++ with added libraries and templates, but in fact the semantics of the two languages end up being very different.

The… Read More

The Accellera Systems Initiative, most well-known for driving the standardization of various aspects of Verilog and SystemVerilog before handing the standards off to the IEEE, has announced that nominations are open for the 2013 Technical Excellence Award. This recognizes outstanding contributions in the creation of EDA… Read More

If verification is the art of determining that your design works correctly under all specified conditions, then it is imperative that we are able to create an environment that can tell you if this is truly the case.

Scoreboards are verification components that determine that the DUT is working correctly, including ensuring that… Read More