Next week is a big deal because it’s when Synopsys has their annual user group meeting, SNUG in Santa Clara at the Convention Center from Monday through Wednesday. I’d love to hear if they have made any decisions on the new product roadmap after the Magma acquisition, although it’s probably too early to tell.… Read More

Tag: synopsys

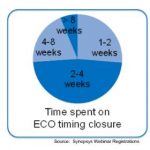

Timing Closure for ECOs in your SOC Design

I decided to attend a webinar today hosted by Synopsys, “Streamline Your PrimeTime ECO Flow For Fastest Setup, Hold and Timing DRC Closure.” The format was to present slides first then hold for questions until the end. Enough time was spent on questions which made this webinar different than most other webinars I’ve… Read More

Common Platform Technology Forum: Peering into the Future

Next Wednesday is the Common Platform Technology Forum. “Common Platform” is a name that only a committee could have come up with, giving no clue as to what it actually is. As you probably know, there are various process clubs sharing the costs of technology development (TD) and one of them consists of IBM, Samsung and… Read More

IC Custom IP Blocks – EM and IR Drop Effects

Designing custom IP blocks is a challenge at the transistor-level and I wanted to learn what the recommended methodology and EDA tool flow was at Synopsys. They have a webinar that you can register for and it takes 30 minutes to learn what they have to say, or you can read a White Paper. If you cannot spare that much time, then my summary… Read More

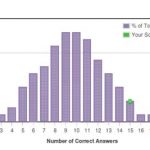

Test Synopsys offensive in VIP and try the quiz

I have recently blogged about Synopsys offensive in the Verification IP market. Did Synopsys again launched a new product, or announced a new acquisition? This would be a serious topic to blog, but today’s blog is closer to gaming than market analysis. Sometimes it’s good to have fun, even if the topic is serious! In fact, Synopsys… Read More

Designing ARM Powered High Performance SoCs on 28nm and 20nm!

Last week I had an interesting meeting with GLOBALFOUNDRIES executives Kevin Meyer and Mojy Chian. It certainly seems that GFI has turned a corner! I will be in Dresden next week for DATE 2012 and will also visit the GFI Fab there. 28nm and 20nm are on track so expect an aggressive implementation plan from GFI this year.… Read More

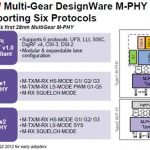

Synopsys MIPI M-PHY in 28nm introduction with Arteris

MIPI set of specifications (supported by dedicated controllers) are completed by a PHY function, the D-PHY or the M-PHY function. The D-PHY was the first to be released, and most of the MIPI functions supported in a smartphone we are using today probably still use a D-PHY, but the latest MIPI specifications have been developed based… Read More

HSPICE Users Talking about Their Circuit Simulation Experience, Part 2

Continued from < Part 1 <… Read More

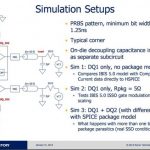

HSPICE Users Talking about Their Circuit Simulation Experience

HSPICE users gathered in January 2012 at the HSPICE SIG(Special Interest Group) to talk about their experiences using this circuit simulator for a variety of IC and signal integrity issues. I wasn’t able to attend in person however I did watch the video and wanted to summarize what I heard:… Read More

Yalta is Dead! Synopsys offensive in VIP restart the cold war

Last year, you could claim (like I did in this blog) that Cadence was making money with large VIP port-folio, when Synopsys was managing sales of a large Design IP port-folio (thanks to a successful acquisition strategy in the 2000’s). But the latest acquisitions made by Synopsys of VIP centric companies like nSys or ExpertIO should… Read More