You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

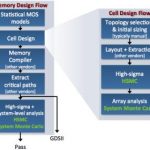

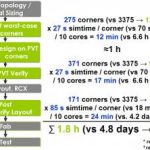

Solido Design Automation and TSMC recently published an article in EE Times describing how Solido’s High-Sigma Monte Carlo tool is used with TSMC PDK’s to achieve high-yield, high-performance memory design. This project has been a big part of my life for the past three years and it is time for a victory lap!

In TSMC 28nm, 20nm and … Read More

I met with Amit Gupta, President and CEO of Solido at DAC on Tuesday to get an update on their EDA tools used in the design of memory, standard cells and low-power. In 2012 they’ve expanded to add three new software packages: Memory, Standard Cell, Low Power. They must be doing something right because at DAC this year I see more… Read More

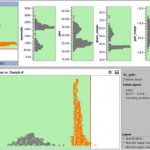

On Wednesday there is a User Track Poster Session that examines the design impact of process variation in GLOBALFOUNDRIES 28nm technology. For those of you who are wondering what process variation looks like at 20nm take this 28nm example and multiply it by one hundred (slight exaggeration, maybe).

Variation effects have a significant… Read More

Having spent a considerable amount of time with Solido, they were one of the founding members of SemiWiki, I can tell you that at 20nm the Variation Designer Platform is a critical part of the emerging 20nm design methodology. You can read more on Solido’s SemiWiki landing page HERE. It is well worth the click.

With technology… Read More

Hello Daniel,

I am very interested on the articles on the PVT simulation, I have worked in that area in the past when I worked in process technology development and spice modeling and I also started a company called Device modeling technology (DMT) which built a Spice model library of discrete components, such as Bipolar/MOS /POWER… Read More

Solido has announced webinars for North America, Europe and Asia on October 12-13. They will be describing the variation analysis and design solutions in the TSMC AMS Reference Flow 2.0 announced at the Design Automation Conference this year.

“We are pleased to broaden our collaboration with Solido in developing advanced variation… Read More

On Sept 22, 2011, the nm Circuit Verification Forumwill be held in Silicon Valley, hosted by Berkeley Design Automation. At this forum, Trent McConaghy of Solido DA will present a case study on the TSMC Reference Flow 2.0 VCO circuit, to showcase Fast PVT in the steps of extracting PVT corners, verifying PVT, and doing post-layout… Read More

Whether you use a gate-first or gate-last High-k Metal Gate implementation, yield will be your #1 concern at 28nm, which makes variation analysis and verification a big challenge. One of the consulting projects I have been working on with the foundries and top fabless semiconductor companies is High-Sigma Monte Carlo (HSMC) … Read More

Introduction

When I designed DRAM chips at Intel I wanted to simulate at the worst case process corners to help make my design as robust as possible in order to improve yields. My manager knew what the worst case corners were based on years of prior experience, so that’s what I used for my circuit simulations.… Read More