In principle, one way to address variation is to do simulations at lots of PVT corners. In practice, most of this simulation is wasted since it adds no new information, and even so, important corners will get missed. This is what Sifuei Ku of Microsemi calls the British Museum Algorithm. You walk everywhere. And if you don’t walk to… Read More

Tag: solido

Solido Wrote the Book on Variation

When I studied mathematical analysis, one of the things that we had to prove turns out to be surprisingly difficult. If you have a continuous function and at one point it is below a line (say zero) and at another point it is above zero, then there must be a point at which the value is exactly zero. In effect, a continuous function can’t… Read More

Designing for Variation

There is a widespread phenomenon in designing chips that new effects creep up on you. First they are so small you can ignore them. Then you can add a little pessimism to your timing budget or whatever gets affected. But eventually the effects go from second order to first order. You certainly can’t ignore them, and the guard … Read More

High-Sigma Standard Cell Optimization!

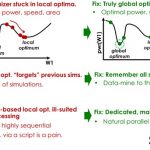

Standard cell optimization is an important problem, because the speed, power, and area of cells has a direct impact speed, power, and area of the whole chip. Typically, standard cell optimization been done with simple in-house local-optimizer scripts. However, these optimizers have had several flaws: they don’t properly capture… Read More

SemiWiki Top 10 Must See @ #50DAC List!

This list was compiled by the SemiWiki bloggers highlighting emerging technologies that we have written about and that will be demonstrated at the Design Automation Conference next week. We highly recommend you investigate them further during your time in Austin and please let us know what you think.

Today SemiWiki has more than… Read More

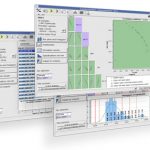

BDA Introduces High-Productivity Analog Characterization Environment (ACE)

Last week Berkeley Design Automation introduced a new Analog Characterization Environment (ACE) – a high-productivity system to ensure analog circuits meet all specifications under all expected operational, environmental, and process conditions prior to tapeout.

While standard cell characterization and memory characterization… Read More

#50DAC: Winning in Monte Carlo!

One of the places you will be able to find me at the Design Automation Conference (DAC) is on the speaker panel for a Monday Tutorial – Winning in Monte Carlo: Managing Simulations Under Variability and Reliability. Having worked closely with TSMC, GLOBALFOUNDRIES, Solido Design Automation, and some of the top fabless semiconductor… Read More

Solido CEO on 20nm/16nm TSMC and GLOBALFOUNDRIES Design Challenges

EDA needs more CEOs like Amit Gupta. Solido, which is now profitable, is his second AMS EDA company. The first, Analog Design Automation (ADA), was purchased by Synopsys for a hefty multiplier. Prior to becoming an EDA entrepreneur, Amit was product manager for the wireless group at Nortel and a hardware engineer for the RF communications… Read More

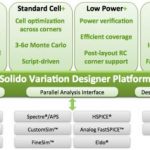

TSMC ♥ Solido

Process variation has been a top trending term since SemiWiki began as a result of the articles, wikis, and white papers posted on the Solido landing page. Last year Solido and TSMC did a webinar together, an article in EETimes, and Solido released a book on the subject. Process variation is a challenge today at 28nm and it gets worse… Read More

Variation-Aware Design: A Hands-on Field Guide

IC designers using advanced nodes are acutely aware of how variation effects in the silicon itself are causing increased analysis and design efforts in order to yield chips at acceptable levels. Four authors from Solidoare so passionate about this topic that they combined their years of experience into a book that I had a chance… Read More