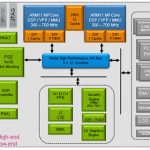

Most SoC designs these days consist largely, but not entirely, of purchased IP blocks. But there are lots of tradeoffs involved in selecting IP blocks, and since those tradeoffs change with process node, even decisions that seem “obvious” based on the last generation of the design, may not be so clear cut. Even if you… Read More

Tag: semiconductor

GSA European Executive Forum

The first week of June is DAC in Austin of course. But over in Europe, the Wednesday and Thursday of that week, June 5-6th is the GSA European Executive Forum, bringing C-level executives together from all over Europe. It actually runs from 2pm on Wednesday until about 2pm on Thursday including a VIP dinner on Wednesday evening sponsored… Read More

Best Practice for RTL Power Design for Mobile

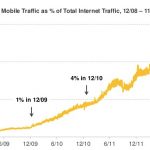

Mobile devices are taking over the world. If you want lots of graphs and data then look at Mary Meeker’s presentation that I blogged about earlier this week. The graph on the right is just one datapoint, showing that mobile access to the internet is probably up to about 15% now from a standing start 5 years ago.

Of course, one obvious… Read More

ESD – Key issue for IC reliability, how to prevent?

It’s a common electrical rule that when large amount of charge gets accumulated, it tries to break any of its surrounding isolation. Although it wouldn’t have been prominent in 1980s or 90s, protection for ICs from such damaging effects is a must, specifically in large mixed-signal designs of today, working at different voltages… Read More

Happy Birthday to Synopsys VIP

I met Mike Sanie around DVCon time and planned to write a blog about the one year anniversary of Synopsys Discovery VIP which was announced during Aart’s keynote at DVCon in 2012. Eric covered it for SemiWiki here. But Synopsys had other stuff they wanted me to blog about and so it is a couple of months late. The 14th month anniversary… Read More

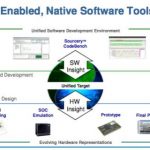

Mentor’s New Embedded Strategy

If there is a trend I can detect in verification in 2013, it is taking verification environments and making the user interface, scripts, and tools work uniformly across the whole spectrum of possible verification “substrates” from virtual platforms, FPGA boards, emulation, actual chips, RTL simulation and so … Read More

A Brief History of Methodics

Methodics was founded in 2006 by 2 ex-Cadence experts in the Custom IC design tools space, Simon Butler and Fergus Slorach. They had a consulting company called IC Methods, active in Silicon Valley from 2000-2006, and when they needed to create a new company to service a consulting engagement that had turned into a product, they … Read More

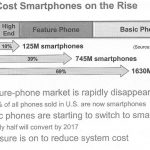

Linley Mobile

I was at the Linley Mobile Microprocessor conference earlier in the week. Well, just the first day since the second day overlapped with the GSA Silicon Summit. The first surprise was seeing Mike Demler in a suit. It turns out that he has joined the Linley Group as a full-time analyst in the mobile space.

Linley Gwennap started the day… Read More

Moore, or More Than Moore?

Yesterday was the 2013 GSA Silicon Summit, which was largely focused on contrasting what advances in delivering systems will depend on marching down the ladder of process nodes, and which will depend on innovations in packaging technology. So essentially contrasting Moore’s Law with what has come to be known as More Than… Read More

On Resistive RAM Product Announcements and Meetings

A lot has been happening in the ReRAM world over the past couple of months. At the ISSCC Conference in February Toshiba/SanDisk presented a paper describing a 32Gbit ReRAM chip.… Read More