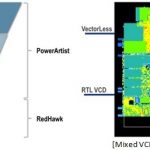

Last month in DAC I could see some of the top innovations in the EDA world. EDA is a key enabler for advances in semiconductor designs. Among a number of innovations worth mentioning (about which I blogged just after DAC), the integration of Mentor’s Veloce with ANSYS’ PowerArtist for power analysis of live applications caught my… Read More

Tag: rpm

Noise & Reliability of FinFET Designs – Success Stories!

I think by now there has been good level of discussion on FinFET technology at sub-20 nm process nodes and this is an answer to ultra dense, high performance, low power, and billion+ gate SoC designs within the same area. However, it comes with some of the key challenges with respect to power, noise and reliability of the design. A FinFET… Read More

How to meet 3Ps in 3D-ICs with sub-20nm Dies?

It feels to be at the top of semiconductor technology by having dies with high density of semiconductor design at sub-20nm technology node stacked together into a 3D-IC to form a complete SoC which can accommodate billions of gates. However there are multiple factors to be looked at in order to make that successful amid often conflicting… Read More

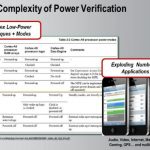

How to Assure Quality of Power and SI Verification?

As power has become one of the most important criteria in semiconductor design today, I was wondering whether there is a standard set for the power verification for an overall chip. We do have formats evolved like CPF and UPF and there are tools available to check power and signal integrity (SI), however I don’t see a standard objective… Read More

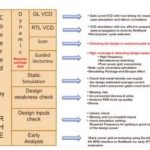

Apache Power Artist Capabilities II

This is the second part of my discussion with Paul Traynar, Apache’s PowerArtist guru. The first part discussed sequential reduction capabilities. Part I was here.

There are two big challenges with doing power analysis at the RTL level. Firstly, how do you get an accurate enough model of what the design will dissipate given… Read More

RTL Power Models

One of the challenges of doing a design in the 28nm world is that everything depends on everything else. But some decisions need to be made early with imperfect information. But the better the information we have, the better those early decisions will be. One area of particular importance is selecting a package, designing a power… Read More