I met with Amit Gupta, President and CEO of Solido at DAC on Tuesday to get an update on their EDA tools used in the design of memory, standard cells and low-power. In 2012 they’ve expanded to add three new software packages: Memory, Standard Cell, Low Power. They must be doing something right because at DAC this year I see more… Read More

Tag: process variation

TSMC Threater Presentation: Solido Design Automation!

For a small company, Solido has some very large customers and partners, TSMC being on of them. Why? Because of the high yield and memory performance demand on leading edge technologies, that’s why.

Much has been made of and will continue to be said on the march of Moore’s Law. While economics of scale and performance vs. power… Read More

Understanding and Designing For Variation in GLOBALFOUNDRIES 28nm

On Wednesday there is a User Track Poster Session that examines the design impact of process variation in GLOBALFOUNDRIES 28nm technology. For those of you who are wondering what process variation looks like at 20nm take this 28nm example and multiply it by one hundred (slight exaggeration, maybe).

Variation effects have a significant… Read More

Solido Design Automation Update 2012

Having spent a considerable amount of time with Solido, they were one of the founding members of SemiWiki, I can tell you that at 20nm the Variation Designer Platform is a critical part of the emerging 20nm design methodology. You can read more on Solido’s SemiWiki landing page HERE. It is well worth the click.

With technology… Read More

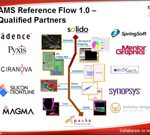

High-efficiency PVT and Monte Carlo analysis in the TSMC AMS Reference Flow for optimal yield in memory, analog and digital design!

Hello Daniel,

I am very interested on the articles on the PVT simulation, I have worked in that area in the past when I worked in process technology development and spice modeling and I also started a company called Device modeling technology (DMT) which built a Spice model library of discrete components, such as Bipolar/MOS /POWER… Read More

Solido & TSMC Variation Webinar for Optimal Yield in Memory, Analog, Custom Digital Design

Solido has announced webinars for North America, Europe and Asia on October 12-13. They will be describing the variation analysis and design solutions in the TSMC AMS Reference Flow 2.0 announced at the Design Automation Conference this year.

“We are pleased to broaden our collaboration with Solido in developing advanced variation… Read More

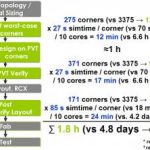

PVT and Statistical Design in Nanometer Process Geometries

On Sept 22, 2011, the nm Circuit Verification Forumwill be held in Silicon Valley, hosted by Berkeley Design Automation. At this forum, Trent McConaghy of Solido DA will present a case study on the TSMC Reference Flow 2.0 VCO circuit, to showcase Fast PVT in the steps of extracting PVT corners, verifying PVT, and doing post-layout… Read More

Variation Analysis

I like to say that “you can’t ignore the physics any more” to point out that we have to worry about lots of physical effects that we never needed to consider. But “you can’t ignore the statistics any more” would be another good slogan. In the design world we like to pretend that the world is pass/fail. But manufacturing is actually a statistical… Read More

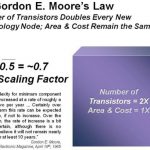

Moore’s Law and Semiconductor Design and Manufacturing

The semiconductor design and manufacturing challenges at 40nm and 28nm are a direct result ofMoore’s Law, the climbing transistor count and shrinking geometries. It’s a process AND design issue and the interaction is at the transistor level. Transistors may be shrinking, but atoms aren’t. So now it actually matters when even… Read More

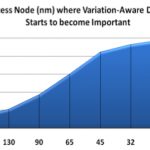

Variation-aware Design Survey

Solidohas run an interesting survey on variation-aware design. The data is generic and not specific to Solido’s products although you won’t be surprised to know that they have tools in this area.

What is variation-aware design? Semiconductor manufacturing is a statistical process and there are two ways to handle this in the design… Read More