The Phil Kaufman Award has been given annually since 1994 to individuals who have had a significant impact on Electronic System Design. I have attended several of the award dinners during that time. Most of the time (roughly 70%), the award recipients were either people I knew or people whose textbooks I had read. The award goes to… Read More

Tag: power analysis

Accurate Power Sooner

Synopsys PrimeTime PX, popularly known as PT-PX, is widely recognized as the gold standard for power signoff. Calculation is based on a final gate-level netlist reflecting final gate selections and either approximate interconnect parasitics or final parasitics based on the post-layout netlist. The only way to get more accurate… Read More

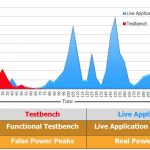

Getting the Best Dynamic Power Analysis Numbers

On your last SoC project how well did your dynamic power estimates match up with silicon results, especially while running real applications on your electronic product? If your answer was, “Well, not too good”, then keep reading this blog. A classical approach to dynamic power analysis is to run your functional testbench… Read More

Power and Thermal Analysis of Data Center and Server ICs

The server market is a diverse, yet standardized market. The ICs and components designed and manufactured in final assemblies must meet form factor requirements for rack mount and blades. The form factor enclosures and the component placement dictate the thermal-mechanical properties and hence the thermal cooling limits … Read More

Non-separation of power and performance

How much power does a system consume? The simplistic path to power estimation for a system used to be tossing a few metrics – standby, typical, worst case, with figures pulled from a datasheet, simulation, or physical measurement – into a spreadsheet. After filling the remaining holes with SWAG (scientific wild-ass guesses), … Read More

Different Approaches to System Level Power Modeling and Analysis for Early Design Phases

At DATEthis year in Dresden, Bernhard Fischer from Siemens CT(Corporate Technology) has presented an interesting summary of the various techniques used for power modeling and analysis at the architectural level. He went through the pros and cons of using spreadsheets, timed virtual platforms annotated with power numbers … Read More

Acquiring Great Power

“Before we acquire great power we must acquire wisdom to use it well”

Ralph Waldo Emerson

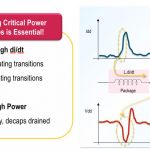

Making good architectural decisions for controlling power consumption and ensuring power integrity requires a good analysis of the current requirements and how they vary. Low power designs, and today there really aren’t… Read More

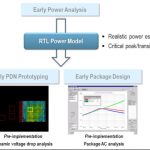

RTL Power Models

One of the challenges of doing a design in the 28nm world is that everything depends on everything else. But some decisions need to be made early with imperfect information. But the better the information we have, the better those early decisions will be. One area of particular importance is selecting a package, designing a power… Read More

Noise Coupling

One of the challenges of designing a modern SoC is that the digital parts of the circuit are really something that in an ideal world you’d keep as far away from the analog as possible. The digital parts of the circuit generate large amounts of noise, especially in the power supply and in the substrate, two areas where it is impossible… Read More

First low-power webinar: Ultra-low-power Methodology

The first of the low power webinars is coming up on July 19th at 11am Pacific time. The webinar will be conducted by Preeti Gupta, Sr. Technical Marketing Manager at Apache Design Solutions. Preeti has 10 years of experience in the exciting world of CMOS power. She has a Masters in Electrical Engineering from Indian Institute of technology,… Read More