In the rapidly evolving world of high-performance computing (HPC) and artificial intelligence (AI), technological advancements must keep pace with increasing demands for speed, efficiency, and security. Synopsys recently announced the industry’s first complete PCIe 7.0 IP solution. This groundbreaking initiative addresses… Read More

Tag: PAM 4

Demand for High Speed Drives 200G Modulation Standards

Right now, the most prevalent generation of Ethernet for data centers is 400 Gbps, with the shift to 800 Gbps coming rapidly. It is expected that by 2025 there will be 25 million units of 800 Gbps shipped. Line speeds of 100G are used predominantly for 400 Gbps Ethernet – requiring 4 lanes each. Initially 800 Gbps will simply … Read More

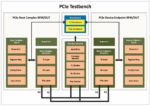

PCIe Gen 6 Verification IP Speeds Up Chip Development

PCIe is a prevalent and popular interface standard that is used in just about every digital electronic system. It is used widely in SOCs and in devices that connect to them. Since it was first released in 2003, it has evolved to keep up with rapidly accelerating needs for high speed data transfers. Each version has doubled in throughput,… Read More

PCIe 6.0 Doubles Speed with New Modulation Technique

PCI-SIG has held to doubling PCIe’s data rate with each revision of the specification. The consortium of 800 companies, with its board consisting of Agilent, AMD, Dell, HP, Intel, Synopsys, NVIDIA, and Qualcomm, is continuing this trend with the PCIe 6.0 specification which calls for a transfer rate of 64 GT/s. PCI-SIG released… Read More

How PCI Express 6.0 Can Enhance Bandwidth-Hungry High-Performance Computing SoCs

What do genome sequencing, engineering modeling and simulation, and big data analytics have in common? They’re all bandwidth-hungry applications with complex data workloads. High-performance computing (HPC) systems deliver the parallel processing capabilities to generate detailed and valuable insights from these applications.

eSilicon’s Latest SerDes Solution is Here – And It Took A Village

I recently watched a webinar given by eSilicon about its project to enhance its licensable solution for 56 and 112 Gigabit per second PAM4 & NRZ DSP-based SerDes family in 7nm. I am sure it was complicated enough to coordinate a webinar with a host, a moderator, and three different technical presenters – however when we are talking… Read More

Monday DAC IP Session “PAM 4 Enable 112G SerDes”

This session will open the DAC IP Track at 10:30 on Monday “How PAM4 and DSP Enable 112G SerDes Design” in Room N264. I am very proud to chair this invited paper session, as it addresses one of the key pieces of design, enabling to exchange data flow at the highest possible data rate. It can be between two chips on the same board, we talk … Read More