Using chiplets is an emerging trend well-covered at #62DAC and they even had a dedicated Chiplet Pavilion, so I checked out the presentation from Dan Slocombe, Design Engineering Architect in the Compute Solutions Group at Cadence. In a short 20 minutes Dan managed to cover a lot of ground, so this blog will summarize the key points.… Read More

Tag: palladium

Cadence Dynamic Duo Upgrade Debuts

Cadence calls their hardware acceleration platforms, Palladium Z2 for fast pre-silicon hardware debug and Protium X2 for fast pre-silicon software validation, their Dynamic Duo. With good reason. Hardware acceleration is now fundamental to managing the complexity of verification and validation for large systems, hardware… Read More

Imperas and RISC-V

I met Imperas at TechCon this year because I wanted to become a bit more knowledgeable about virtual modeling. That led me to become more interested in RISC-V and a talk given by Krste Asanovic of UCB and SiFive. My takeaway surprised me. I had thought this was an open-source David versus proprietary Goliaths (Intel and ARM) battle… Read More

Blurring Boundaries

I think most of us have come to terms with the need for multiple verification platforms, from virtual prototyping, through static and formal verification, to simulation, emulation and FPGA-based prototyping. The verification problem space is simply too big, in size certainly but also in dynamic range, to be effectively addressed… Read More

System-Level Power Estimation

When I first saw that Rob Knoth (Product Director at Cadence) had proposed this topic as a subject for a blog, my reaction was “well, how accurate can that be?” I’ve been around the power business for a while, so I should know better. It’s interesting that I jumped straight to that one metric for QoR; I suspect many others will do the same.… Read More

Prototyping: Sooner, Easier, Congruent

DVCon 2017 is a big week for Cadence verification announcements. They just released their Xcelium simulation acceleration product (on which I have another blog) and they have also released their latest and greatest prototyping solution in the Protium S1. This is new hardware based on Virtex UltraScale FPGAs on Cadence-designed… Read More

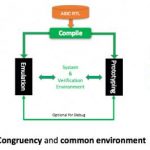

Aspirational Congruence

When talking to suppliers about their products, conversation tends to focus heavily on what they already have and why it is the answer to every imaginable need in their space. So it’s refreshing when a vendor wants to talk about where customers want to go without claiming they already have the answer wrapped up in a bow. I recently … Read More

Protium for the win in software development

Cadence Design Systems is a long-standing provider in hardware emulation, but a relative newcomer to FPGA-based prototyping. In an upcoming lunch and learn session on November 11 in San Jose, Cadence teams will be outlining their productivity strategy. What’s different with their approach and why is this worth a lunch?… Read More

Software-Driven Verification Drives Tight Links between Emulation and Prototyping

I’ve mentioned many times what has become a very common theme in SoC and system verification – it has to be driven by the software because any concept of exhaustively verifying “everything” is neither feasible nor meaningful. Emulation has become a critical component of this flow in validating and regressing… Read More

Palladium Moves Power (and Temperature) Modeling to the System Level

I had a debate with Steve Carlson of Cadence earlier in the year at the EDPS conference on whether there were really any truly effective solutions for doing power estimation in emulation. I thought there weren’t and he said I was wrong. After attending the Cadence front-end summit last week, I have to admit he has a point.

First, who… Read More