IBM last week agreed to transfer its semiconductor business to GlobalFoundries. GlobalFoundries will acquire wafer fabs in East Fishkill, New York and Essex Junction, Vermont; IBM’s commercial microelectronics business, which includes ASIC and foundry; over 10,000 IBM patents related to semiconductor manufacturing;… Read More

Tag: nxp

AMD Design IP Deal with Virage Logic… Oops… Synopsys

Whoever has said that history never repeats itself should read this recent PR from AMD! The news can be summarized in three points:

- Multi-year agreement gives AMD access to a range of Synopsys design IP including interface, memory compiler, logic library and analog IP for advanced FinFET process nodes

- Synopsys acquires rights

Noise-Coupled Analysis for Automotive ICs at DAC

My favorite method to learn about EDA tools at DAC is by listening to actual IC designers, so on June 3rd I heard Jacob Bakker from NXP talk about his experience with noise coupled analysis for advanced mixed-signal automotive ICs.… Read More

RedHawk Excels – Customers Endorse

Since a few years, I have been following up Ansys Apachetools for semiconductor design, verification and sign-off. RedHawk is the most prominent platform of tools from Ansys, specifically for Power, Noise and Reliability Sign-off. It has witnessed many open endorsements from several of Ansyscustomers through open presentations,… Read More

Fab-U-Less! The 2013 Global Semiconductor Awards!

It was a dinner with more than a thousand semiconductor professionals from around the world keynoted by Author and Editor in Chief of Forbes Magazine Steve Forbes. What more could a humble blogger ask for? Even at $250 a plate it was well worth it just to mingle amongst the people who make this industry so great.

Global Semiconductor… Read More

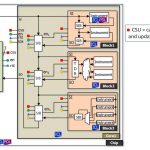

Mentor and NXP Demonstrate that IJTAG Can Reduce Test Setup Time for Complex SoCs

The creation of test patterns for mixed signal IP has been, to a large extent, a manual effort. To improve the process used to test, access, and control embedded IP, a new IEEE P1687 standard is being defined by a broad coalition of IP vendors, IP users, major ATE companies, and all three major EDA vendors. This new standard, also called… Read More