There is never enough memory bandwidth. Well, occasionally there is but many SoCs have lots of blocks that communicate through memory, typically off-chip DRAM. In 2001 Sonics created their first solution to this problem with MemMax technology that was incorporated into their SonicsSX product. This has been used in over 100 designs… Read More

Tag: network on chip

Sonics and Qualcomm Make a Deal

Some background. Sonics has been in the network-on-chip (NoC) business for a long time. Nearly 18 years years. When Arteris launched their products, Sonics figured Arteris were infringing Sonics’s patents and in 2011 brought a complaint against them. Details are here. Arteris looked at a couple of their own patents (if… Read More

A song of optimization and reuse

If you hang around engineers for any time at all, the word optimization is bound to come up. The very definition of engineer is to contrive or devise a solution. With that anointing, most engineers are beholden to the idea that their job is creating, synthesizing, and perfecting a solution specifically for the needs of a unique situation.… Read More

Sensor clusters at edge call for NoCs nearby

In his recent blog on EETimes, Kurt Shuler of Arteris took a whimsical look at the hype surrounding the IoT, questioning the overall absence of practicality and a seemingly misplaced focus on use cases at the expense of a coherent architecture. I don’t think it is all that bleak, but when it comes to architecture, Kurt is right, and… Read More

The (re)making of Arteris, 1-2-3

Success in a business with extended design-in cycles may look easy. In reality, there is a delicate balance between many factors. Some come to mind immediately: developing and releasing a good product in the first place; winning and keeping the right customers, not too few or too many; balancing investment between support and … Read More

Compositions allow NoCs to connect easier

I blame it on Henry Ford, William Levitt, and the NY State Board of Regents, among others. We went through a phase with this irresistible urge to stamp out blocks of sameness, creating mass produced clones of everything from cars to houses to students.

Thank goodness, that’s pretty much over. The thinking of simplifying system design… Read More

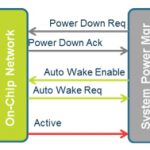

5 Rules of Power Management Using NoCs

If it has escaped your notice that power management on SoCs is important then you need to get out more. Increasingly, the complexity of the interconnect between the various processors, memories, offload processors, devices, interfaces and other blocks means that the best way to implement it is to use a network on chip (NoC). But… Read More

Qualcomm and Arteris: the CEO Speaks

Arteris finally announced this morning, as rumored, that Qualcomm is acquiring “certain technology assets” and hired personnel formerly employed by Arteris. The financial terms were not disclosed.

I talked to Charlie Janac, the CEO, today. The first thing I asked him is why such a convoluted deal, I’ve never… Read More

Qualcomm Arteris deal

Is it really a surprise if Qualcomm, the undisputed leader of Application Processor (AP) and BaseBand (BB) IC for wireless mobile, already one of the Arteris investors (with ARM, Synopsys, Docomo Capital and a bunch of VC), eventually acquires the best NoC IP technology (the technology, the engineering team and the rights, but… Read More

Open Letter from Sonics to Arteris

I don’t remember seeing an open letter from one EDA or IP company to another until today. Sonics have published an open letter to Charlie Janac, the CEO of Arteris. What seems to have happened is that Arteris have sold their assets to Qualcomm and the development team (which is based in France) and several AEs are already Qualcomm… Read More