Semiconductor intellectual property (IP) plays a critical role in modern system-on-chip (SoC) designs. That’s not surprising given that modern SoCs are highly complex designs that leverage already proven building blocks such as processors, interfaces, foundational IP, on-chip bus fabrics, security IP, and others. This… Read More

Tag: memories

Upcoming Webinar on Resistive RAM (ReRAM) Technology

On-chip memory (embedded memory) makes computing applications run faster. In the early days of the semiconductor industry, the desire to utilize large amount of on-chip memory was limited by cost, manufacturing difficulties and technology mismatches between logic and memory circuit implementations. Since then, advancements… Read More

From Medical and Wearables to Big Data, in 日本語/한국어/中文

Whether it’s a tiny always-on medical device or a secure cloud network processing Big Data, the Internet of Things (IoT) is bringing new challenges to IC design. Almost by definition an IoT device contains a microcontroller of some sort along with some way of communicating. Unlike our smartphones where we are reasonably happy … Read More

eSilicon’s IP Marketplace

eSilicon engages with customers in many different ways, from providing a full menu of design services down to simply manufacturing parts. Increasingly, they have been automating a lot of this on their website. It started with automatic quotes for MPW shuttles and more recently they have a full production quote system for parts… Read More

Reducing Dynamic and Static Power in Memories

Sequential approaches to power reduction work well on logic implemented using standard cells. But part of every SoC, sometimes a very large part, is taken up with embedded memories for which alternative approaches are required. Not only do these memories occupy up to half of the area they also account for as much as 75% of the power… Read More

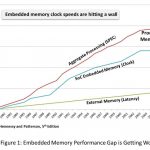

Mind the Gap — Overcoming the processor-memory performance gap to unlock SoC performance

Remember the processor-memory gap— a situation where the processor is forced to stall while waiting for a memory operation to complete? This was largely a result of the high latency required for off chip memory accesses. Haven’t we solved that problem now with SoCs? SoCs are typically architected with their processors … Read More