Much of the technology that goes into aerospace applications is some of the most advanced technology that exists. However, these same systems must also offer the highest level of reliability in what is arguably an extremely difficult environment. For semiconductors a major environmental risk in aerospace applications are … Read More

Tag: iroc

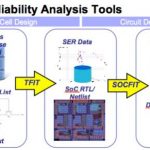

TSMC OIP: Soft Error Rate Analysis

Increasingly, end users in some markets are requiring soft error rate (SER) data. This is a measure of how resistant the design (library, chip, system) is to single event effects (SEE). These manifest themselves as SEU (upset), SET (transient), SEL (latch-up), SEFI (functional interrupt).

There are two main sources that cause… Read More

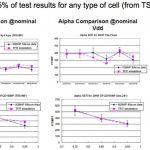

How Resistant to Neutrons Are Your Storage Elements?

There are two ways to see how resistant your designs are to single-event errors (SEE). One is to take the chip or even the entire system and put it in a neutron beam and measure how many problems occur in this extreme environment. While that may be a necessary part of qualification in some very high reliability situations, it is also … Read More

Increase Your Chip Reliability with iROC Tech

As we have moved towards extremely low process nodes with very high chip density, the cost of mask preparation also has become exorbitantly high. It has become essential to know about the failure rates and mitigate the same at the design time before chip fabrication, and also to make sure about chip reliability over time as it is constantly… Read More

Do You Need to Worry About Soft Errors?

As we get down to smaller and smaller process nodes, the problem of soft errors becomes increasingly important. These soft errors are caused by neutrons from cosmic rays, alpha particles from materials used in manufacture and other sources. For chips that go into systems with high reliability this is not something that can be ignored.… Read More

How to Blast Your Chip with High Energy Neutron Beams

So you want to know how reliable your chips are and how susceptible they are to single event effects (SEEs) where a neutron or an alpha particle causes a storage element (flop or memory cell) to flip in a way that alters the behavior of the device. There are two ways a particle hitting a device might not cause a problem. Firstly, the particle… Read More

Cell Level Reliability

I blogged last month about single event effects (SEE) where a semiconductor chip behaves incorrectly due to being hit by an ion or a neutron. Since we live on a radioactive planet and are bombarded by cosmic rays from space, this is a real problem, and it is getting worse at each process node. But just how big of a problem is it?

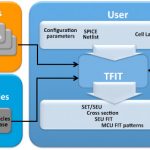

TFIT is … Read More

Soft Error Rate (SER) Prediction Software for IC Design

My first IC design in 1978 was a 16Kb DRAM chip at Intel and our researchers discovered the strange failure of Soft Errors caused by Alpha particles in the packaging and neutron particles which are more prominent at higher altitudes like in Denver, Colorado. Before today if you wanted to know the Soft Error Rate (SER) you had to fabricate… Read More