The semiconductor ecosystem is changing. Monolithic design is becoming multi-die design. Processors no longer inform software development options. It’s now the other way around with complex AI software informing the design of purpose-built hardware. And all that special-purpose hardware needs drivers to make it come to … Read More

Tag: hsi

Webinar: Semifore Offers Three Perspectives on System Design Challenges

The exponential increase in design complexity is a popular topic these days. In fact, it’s been a topic of discussion for a very long time. The explosion of chip and system design complexity over the past ten years has become legendary and haunts many of us daily. A lot of the complexity we face has to do with coordinating across an ever-increasing… Read More

A Solid Methodology is the Margin of Victory

Designing complex systems is difficult. It seems to me that the difficulty has increased at a rate that is more exponential than linear with design complexity. Some version of Moore’s law for design is at work. The challenges for advanced designs just seem to keep mounting. A new item that is top of mind for many executives is the talent… Read More

Register Management is the Foundation of Every Chip

Virtually every chip today runs software. And that software needs to interact with and control the hardware on the chip. There are typically many interfaces to manage as well as dedicated hardware accelerators to coordinate. In fact, many of those hardware accelerators are present only to support the execution of the software… Read More

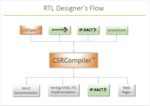

Reusable HW/SW Interface for Portable Stimulus

Although semiconductor community has ushered into the era of SoCs, the verification of SoCs is still broken. There is no single methodology or engine to verify a complete SoC; this results in duplication of efforts and resources for test creation and verification at multiple stages in the SoC development, albeit with different… Read More

CEO Insight: Transformation of Vayavya Labs into System Design Automation

With the advent of SoCs, design abstractions and verification has moved up at the system level. It’s imperative that EDA moves up the value chain to start design automation at system level. The System Design Automation will be the new face of EDA in coming years.… Read More

HW/SW Interfaces for Portable Stimulus

With growing size and complexity of SoC, the semiconductor community is realizing the growing pain of verification. The cost of SoC verification grows exponentially with design size. Moreover, there is no single methodology for verifying a SoC; multiple engines are used in different contexts through different verification… Read More