I’ve been following Solido as a start-up EDA vendor since 2005, then they were acquired by Siemens in 2017. At the recent User2User event there was a presentation by Kwonchil Kang, of Samsung Electronics on the topic, ML-enabled Statistical Circuit Verification Methodology using Solido. For high reliability circuits… Read More

Tag: high sigma

DAC 2021 – Taming Process Variability in Semiconductor IP

Tuesday at DAC was actually my very first time attending a technical session, and the presentation from Nebabie Kebebew, Siemens EDA, was called, Mitigating Variability Challenges of IPs for Robust Designs. There were three presentations scheduled for that particular Designer, IP and Embedded Systems track, but with the COVID… Read More

Webinar on Methods for Monte Carlo and High Sigma Analysis

There is an old saying popularized by Mark Twain that goes “There are three kinds of lies: lies, damned lies, and statistics.” It turns out that no one can say who originated this saying, yet despite however you might feel about statistics, they play an important role in verifying analog designs. The truth is that there are large numbers… Read More

Webinar on Tools and Solutions for Analog IP Migration

The commonly advanced reason for IP reuse is lower cost and shorter development time. However, IP reuse presents its own challenges, especially for analog designs. In the case of digital designs, once a new standard cell library is available, it is usually not too hard to resynthesize RTL to create new working silicon. For analog… Read More

Statistically speaking you probably care about On-chip Variation

There are some metaphorical similarities between reaching timing signoff and driving a car to your destination. Most of us get in the car, turn the key and push the gas pedal to make it go. While we might have a cursory understanding of what makes it go, there are actually a lot of “moving part” under the hood in each instance. For most… Read More

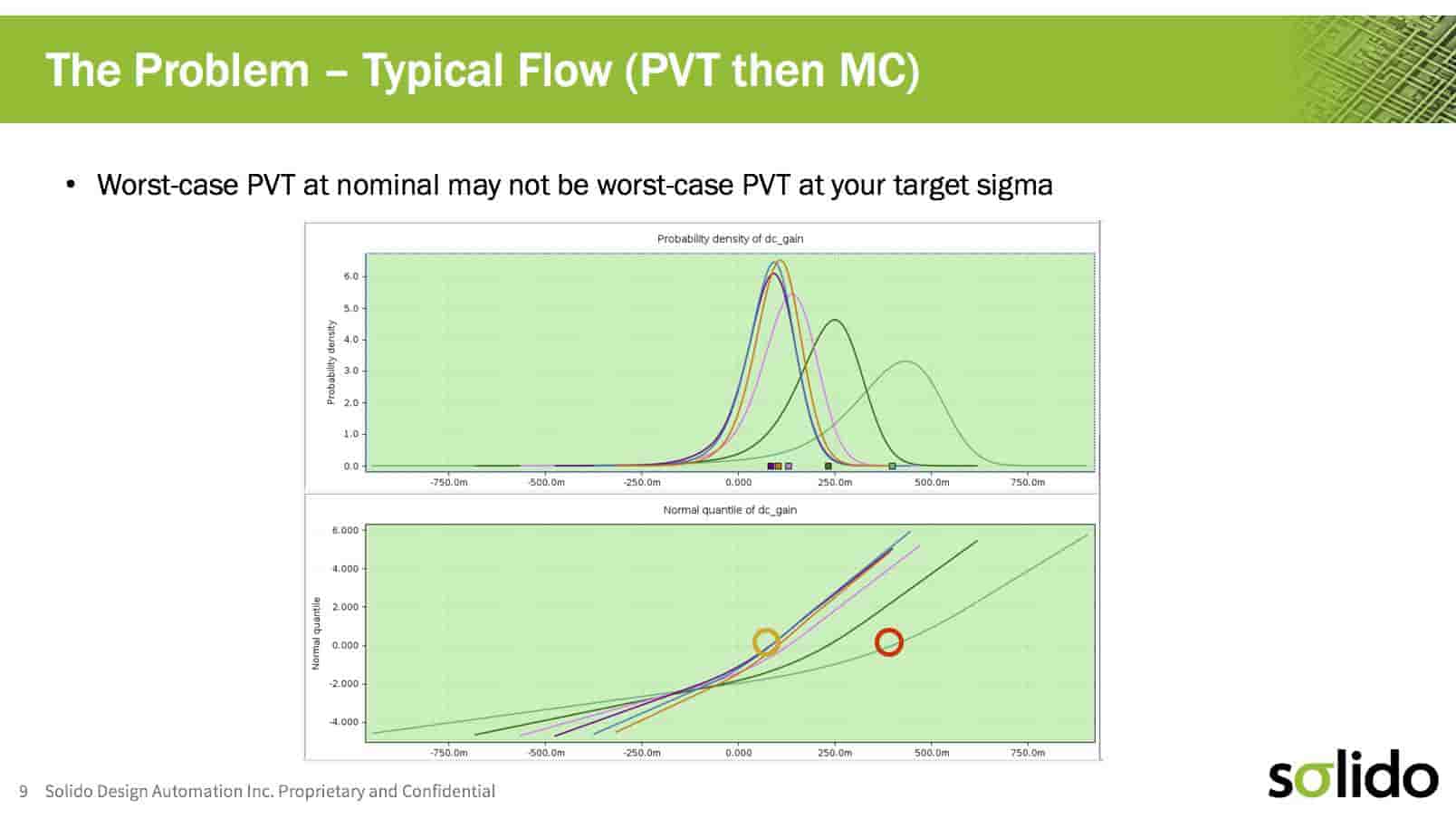

A better way to combine PVT and Monte Carlo to improve yield

TSMC held its Open Innovation Platform Forum the other week on September 13[SUP]th[/SUP]. Each year the companies that exhibit at this event choose to highlight their latest technology. One of the most interesting presentations that I received during the event was from Solido. In recent years they have produced a number of groundbreaking… Read More

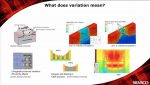

A Better Way for Analog Designers to Perform Variation Analysis

The impact of process variation at advanced nodes is increasing — no surprise there. In recent years, the principal design emphasis to better reflect this variation has been the adoption of two new methodologies: (1) advanced on-chip variation (AOCV, as well as POCV/LVF) for digital static timing analysis, and (2) advanced… Read More

Moving with Purpose for Certainty

In 1492 Christopher Columbus sailed from Spain towards west on Atlantic Ocean in search of Asia and Indies. Between his four voyages (1492 – 1502) he discovered many different islands and then what we call Americas. Although he had a compass with him, imagine searching a needle in a haystack. Even with localization of areas and then… Read More

Designing for Variation

There is a widespread phenomenon in designing chips that new effects creep up on you. First they are so small you can ignore them. Then you can add a little pessimism to your timing budget or whatever gets affected. But eventually the effects go from second order to first order. You certainly can’t ignore them, and the guard … Read More