In a complex environment of semiconductor design where an SoC can have several millions of gates and multiple number of IPs at different levels of abstractions from different sources integrated together, it becomes really difficult to understand and debug the overall SoC design. Of course, along with the SoC integration, optimization… Read More

Tag: gate

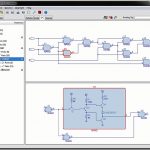

Ten Innovative Debugging Techniques – Pre & Post Layout

In a complex world of SoCs with multi-million gates and IPs from several heterogeneous sources, verification of a complete semiconductor design has become extremely difficult, and it’s not enough. In order to ascertain the right intent of the design throughout the design cycle, debugging at various stages of the design cycle… Read More

Mark your Date for Semiconductor Design Vision

A very popular acronym is ‘WYSIWYG’ – What You See Is What You Get! This is very true and is important to visualize things to make it better in various aspects such as aesthetics, compactness, organization, structure, understandable for correction and so on; the most important, in case of semiconductor design, is being able to identify… Read More

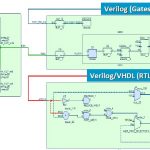

Mixed-Signal SoC Debugging & IP Integration Made Easy

A semiconductor SoC design can have multiple components at different levels of abstractions from different sources and in different languages. While designing an SoC, IPs at different levels have to be integrated without losing the overall design goals. Of course, quality of an IP inside and outside of an SoC must be tested thoroughly.… Read More

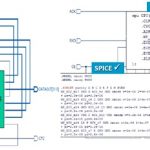

Parasitic Debugging in Complex Design – How Easy?

When we talk about parasitic, we talk about post layout design further expanded in terms of electrical components such as resistances and capacitances. In the semiconductor design environment where multiple parts of a design from different sources are assembled together into highly complex, high density SoC, imagine how complex… Read More