The flexibility of RISC-V processor IP allows much freedom to meet specific requirements – but it also opens the potential for many bugs created during the design process. Advanced processor features are especially prone to errors, increasing the difficulty and time needed for thorough verification. Born out of necessity, … Read More

Tag: formal verification

Podcast EP149: The Corporate Culture of Axiomise with Laura Long

Dan is joined by Laura Long, Director of Business Development at Axiomise. She has over 15 years of experience in business development and has built a strong expertise working with clients with a presence and/or residence in various countries of the European Union, in the UK and in the Americas.

Dan explores the corporate culture… Read More

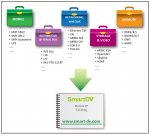

Visual Debug for Formal Verification

Success with Open-Source Formal Verification

The dream of 100% confidence is compelling for silicon engineers. We all want that big red button to push that magically finds all of our bugs for us. Verification, after all, accounts for roughly two-thirds of logic design effort. Without that button, we have to create reference models,… Read More

Intel Best Practices for Formal Verification

Dynamic event-based simulation of RTL models has traditionally been the workhorse verification methodology. A team of verification engineers interprets the architectural specification to write testbenches for various elements of the design hierarchy. Test environments at lower levels are typically exercised then … Read More

Life in a Formal Verification Lane

This summer, I got the opportunity to work as a Formal Verification Intern with Axiomise for six weeks. I’m a keen designer and love working in design and architecture. Although, I’ve not started my professional career yet, I have done most of my projects as a designer in my undergraduate and postgraduate studies.

Having said that,… Read More

Formal Verification Approach Continues to Grow

After a few decades of watching formal verification techniques being applied to SoC designs, it certainly continues to be a growth market for EDA vendors. In the first decades from 1970-1990 the earliest forms of formal tools emerged at technical conferences, typically written by University students earning their Ph.D.s, … Read More

Why I made the world’s first on-demand formal verification course

Verification Challenge

As chip design complexity continues to grow astronomically with hardware accelerators running riot with the traditional hardware comprising CPUs, GPUs, networking and video and vision hardware, concurrency, control and coherency will dominate the landscape of verification complexity for safe … Read More

The Quiet Giant in Verification IP and More

In the technology industry, we’re all used to the hype about the latest and greatest. Semiconductor IP participates in the over-drive news cycle from time to time as well. So, when I see a company that has real, solid credentials but has resisted the temptation to over-hype, it gets my attention. I had an experience like this recently… Read More

Webinar: Finding Your Way Through Formal Verification

Formal verification has always appeared daunting to me and I suspect to many other people also. Logic simulation feels like a “roll your sleeves up and get the job done” kind of verification, easily understood, accessible to everyone, little specialized training required. Formal methods for many years remained the domain of … Read More

Functional Verification using Formal on Million Gate Designs

Verification engineers are the unsung heroes making sure that our smart phone chips, smart watches and even smart cars function logically, without bugs or unintended behavior. Hidden bugs are important to uncover, but what approach is best suited for this challenge?

With the Universal Verification Methodology (UVM) there’s… Read More