IP providers need to evaluate several complex engineering problems when addressing customer requirements – perhaps the most intricate challenge is the degree of IP configurabilityavailable to satisfy unique customer applications. … Read More

Tag: flex logix

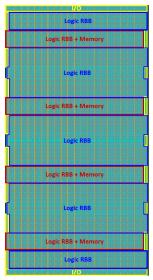

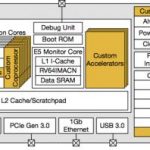

The hierarchical architecture of an embedded FPGA

The most powerful approach to managing the complexity of current SoC hardware is the identification of hierarchical instances with which to assemble the design. The development of the hierarchical design representation requires judicious assessment of the component definitions. The goals for clock distribution, power … Read More

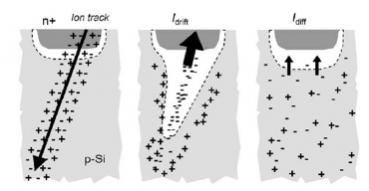

Adapting an embedded FPGA for Aerospace Applications

The IC industry is commonly divided into different market segments – consumer, mobile, industrial, commercial, medical, automotive, and aerospace. A key differentiation among these segments is the characterization and reliability qualification strategy for the fabrication process and design circuitry. For each segment,… Read More

"The Year of the eFPGA" 2017 Recap

This past January, I had postulated that 2017 would be the “Year of the Embedded FPGA”, as a compelling IP offering for many SoC designs (link). As the year draws to a close, I thought it would be interesting to see how that prediction turned out.

The criteria that would be appropriate metrics include: increasing capital investment;… Read More

DesignShare is all About Enabling Design Wins!

One of the barriers to silicon success has always been design costs, especially if you are an emerging company or targeting an emerging market such as IoT. Today design start costs are dominated by IP which is paid at the start of the project and that is after costly IP evaluations and other IP verification and integration challenges.… Read More

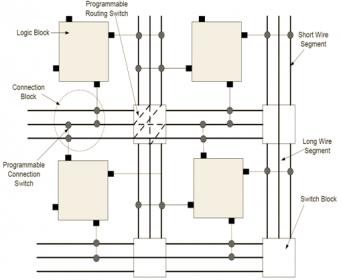

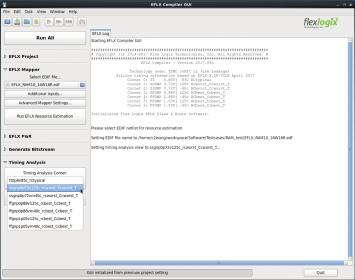

Timing Analysis for Embedded FPGA’s

The initial project planning for an SoC design project faces a difficult engineering decision with regards to the “margin” that should be included as part of timing closure. For cell-based blocks, the delay calculation algorithms within the static timing analysis (STA) flow utilize various assumptions to replace… Read More

Embedded FPGA Blocks as Functional Accelerators (AMBA Architecture, with FREE Verilog Examples!)

A key application for embedded FPGA (eFPGA) technology is to provide functionality for specific algorithms — as the throughput of this implementation exceeds the equivalent code executing on a processor core, these SoC blocks are often referred to as accelerators. The programmability of eFPGA technology offers additional… Read More

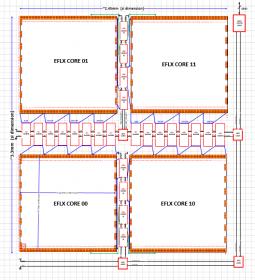

Embedded FPGA IP update — 2nd generation architecture, TSMC 16FFC, and a growing customer base

Regular Semiwiki readers are aware that embedded FPGA (eFPGA) IP development is a rapidly growing (and evolving) technical area. The applications for customizable and upgradeable logic in the field are many and diverse — as a result, improved performance, greater configurable logic capacity/density, and comprehensive… Read More

The eFPGA Market is Heating Up!

It is nice to see an emerging market successfully emerge for a change. With embedded FPGAs we are way past test chips and are now seeing tape-outs and silicon in a variety of applications. I’m not sure what the current market estimate of eFPGA is just yet but they align nicely with the $30B+ micro controller market. Market studies have… Read More

What’s better than silicon-proven IP? Lab bench-proven!

The SoC industry depends upon the availability of validated IP. SoC designs require a huge investment, and assume the external IP that is licensed from outside parties satisfies all functional and electrical specifications. To support that requirement, IP providers typically pursue a strategy to demonstrate their designs… Read More