You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

What an amazing night! I celebrated the 50[SUP]th[/SUP] anniversary of the industry I grew up in! With my beautiful wife at my side and a table full of friends we all went down memory lane, ate, drank, and then enjoyed the auction.

The tour of the new computer museum was amazing. I was learning so much up until the 1970’s, then … Read More

In case you haven’t noticed, Synopsys has been in the press lately talking about their relationship with TSMC. Since I’m an internationally recognized industry expert they gave me a call for a briefing and I was happy to do it. Staying connected with the #1 EDA company is important and fun since I get to ask questions that most people… Read More

For the tenth year, the big 3DIC conference takes place in the Hyatt Regency at Burlingame (just south of San Francisco Airport). Officially it is 3D Architectures for Semiconductor Integration and Packaging or ASIP. This year there have already been some significant 3D announcements: TSMC’s 3D program, and Micron’s… Read More

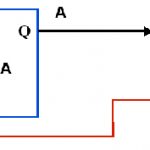

One of the first blogs I wrote on SemiWiki was on clock domain crossing (CDC). I thought it was rather a specialized subject, a sort of minority interest. It turned out to be one of the most-read blogs I’ve written. Modern SoCs have lots of unrelated clocks, maybe hundreds, and so ensuring that signals going from one clock domain… Read More

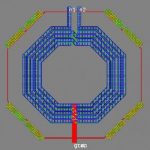

In many designs, an on chip inductor is created as though it were simply a device with an L and a Q value. Of course this view would seem to make life simpler for designers and the tools they use. But in reality even a simple inductor is really a complex compound structure with many electromagnetic elements interacting in complex ways.… Read More

The Biggest Private EDA Companyby admin on 10-21-2013 at 5:02 pmCategories: EDA

I talked this morning with fellow Brit David Halliday. More importantly, he is CEO of Silvaco, which he thinks must be the biggest private EDA company in the world. He didn’t reveal their revenue numbers but they have around 250-300 people and are profitable so you can make your own estimate.

David became CEO when Ivan Pesic,… Read More

The deadline for panel sessions, workshops, tutorials and co-located conferences for DAC 2014 is October 21st. That’s next Monday!

DAC 2014 will not only focus on EDA and embedded systems and software but

also include:

- design methods for automotive systems and software

- hardware and embedded systems security

- IP (semiconductor

…

Read More

One of the benefits of using high-level synthesis is obviously the ease of writing some algorithms in SystemC since it is at a higher level than RTL (that’s why we call it high-level synthesis!). But a second benefit is at the verification level. Since a lot of the verification gets done at the SystemC level, less needs to be done at … Read More

Switched-capacitor (SC) circuits are ubiquitous in CMOS mixed-signal ICs. Thermal noise, introduced by MOS switches and active amplifier circuitry, is the major performance limiter in these circuits. This webinar reviews analysis techniques to accurately analyze the noise performance of switched-capacitor circuits … Read More

The EDA tool space has been booming in this new “mobile era” of computing. As the world transitions to system-on-chip design methodologies, and as more teams are developing even more products for an ever-broadening set of end markets, the demand for ever more sophisticated design tools has only continued to skyrocket.… Read More