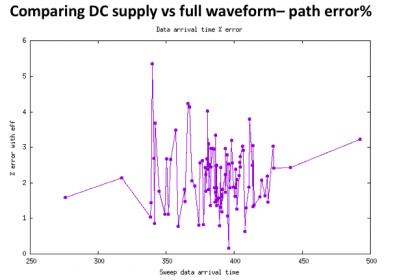

About 6 months ago, ANSYS was approached by a couple of leading mobile platform vendors/suppliers with a challenging problem. These companies were hitting target 2.5GHz performance goals on their (N10 or N7) application processors, but getting about 10% lower yield than expected, which they attributed to performance failures.… Read More

Tag: dvd

Analyze Substrate Noise in SoC Design?

Often substrate noise analysis takes place when everything is there on the chip, but that stage comes near the tape-out which is too late to make major changes in architecture, placement, introducing noise protection circuitry for the victims and so on. It was okay when there used to be very little analog content on the chip. But … Read More

FinFET Based Designs Made Easy & Reliable

Although semiconductor manufacturing has taken off with FinFET based process technology which provides lucrative payoffs on performance improvement, power reduction and area saving in devices for high density and high performance SoC demand of modern era, apprehensions remain about its reliability due to reduced noise … Read More

How to meet 3Ps in 3D-ICs with sub-20nm Dies?

It feels to be at the top of semiconductor technology by having dies with high density of semiconductor design at sub-20nm technology node stacked together into a 3D-IC to form a complete SoC which can accommodate billions of gates. However there are multiple factors to be looked at in order to make that successful amid often conflicting… Read More