Cliff Hou of TSMC gave the keynote today at SNUG on Collaborate to Innovate: a Foundry’s Perspective. Starting around 45nm the way that a foundry has to work with its ecosystem fundamentally changed. Up until then, each process generation was similar enough to the previous one, apart obviously from size, that it could be … Read More

Tag: double patterning

When the lines on the roadmap get closer together

Tech aficionados love roadmaps. The confidence a roadmap instills – whether using tangible evidence or just a good story – can be priceless. Decisions on “the next big thing”, sometimes years and a lot of uncertain advancements away, hinge on the ability of a technology marketing team to define and communicate a roadmap.

Any roadmap… Read More

Virtuoso is 20nm-ready

I already talked about how Cadence is splitting Virtuoso into two. Anyway, it is now officially announced. The 6.1 version will continue to be developed as a sort of Virtuoso classic for people doing designs off the bleeding edge that don’t require the new features. And a new Virtuoso 12.1 intended for people doing 20nm and… Read More

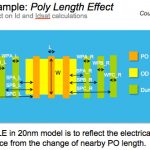

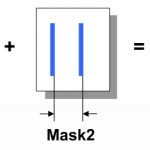

Double Patterning for IC Design, Extraction and Signoff

TSMC and Synopsys hosted a webinar in December on this topic of double patterning and how it impacts the IC extraction flow. The 20nm process node has IC layout geometries so closely spaced that the traditional optical-based lithography cannot be used, instead lower layers like Poly and Metal 1 require a new approach of using two… Read More

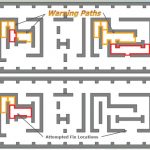

Fixing Double-patterning Errors at 20nm

David Avercrombie of Mentor won the award for the best tutorial at the 2012 TSMC OIP for his presentation, along with Peter Hsu of TSMC, on Finding and Fixing Double Patterning Errors in 20nm. The whole presentation along with the slides is now available online here. The first part of the presentation is an introduction to double … Read More

Mentor @ the TSMC Open Innovation Platform Forum

At TSMC’s Open Innovation Platform (OIP) Ecosystem Forum, Mentor made technical presentations on four different topics, two of them co-presented with TSMC and LSI Corporation. Those presentations are described below with links to downloadable pdf presentation files.

Finding and Fixing Double Patterning Errors in… Read More

Double Patterning Tutorial

Double patterning at 20nm is one of those big unavoidable changes that it is almost impossible to know too much about. Mentor’s David Abercrombie, DFM Program Manager for Calibre, has written a series of articles detailing the multifaceted impacts of double patterning on advanced node design and verification. There is… Read More

Double Patterning Verification

You can’t have failed to notice that 20nm is coming. There are a huge number of things that are different about 20nm from 28nm, but far and away the biggest is the need for double patterning. You probably know what this is by now, but just in case, here is a quick summary.

Lithography is done using 193nm light. Today we use immersion… Read More

Double Patterning Exposed!

Wanna become the double patterning guru at your company? David Abercrombie, DFM Program Manager for Calibre, has written a series of articles detailing the multifaceted impacts of double patterning on advanced node design and verification. For designers struggling to understand the complexity and nuances of double patterning,… Read More

Cadence at 20nm

Cadence has a new white paper out about the changes in IC design that are coming at 20nm. One thing is very clear: 20nm is not simply “more of the same”. All design, from basic standard cells up to huge SoCs has several new challenges to go along with all the old ones that we had at 45nm and 28nm.

I should emphasize that the paper… Read More