Unique device identities are at the core of all computer security systems. Just as important is that each unique identity cannot be copied, because once copied they can be used illegitimately. Unique device IDs are used to ensure that communications are directed to the correct device. And they also provide the ability to encrypt… Read More

Tag: device

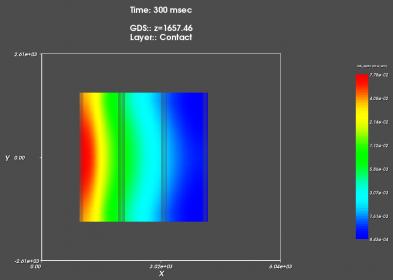

Coupled Electro-thermal Analysis Essential for PowerMOS Design

Power device designers know that when they see a deceptively simple pair of PowerMOS device symbols in the output stage of a power converter circuit schematic, they are actually looking at a massively complex network of silicon and metal interconnect. The corresponding physical devices can have a total device W on the order of … Read More

HW/SW Interfaces for Portable Stimulus

With growing size and complexity of SoC, the semiconductor community is realizing the growing pain of verification. The cost of SoC verification grows exponentially with design size. Moreover, there is no single methodology for verifying a SoC; multiple engines are used in different contexts through different verification… Read More