Anybody who has done any bus & board system design knows the problem. Merchant boards typically have standardized pinouts (after years of haggling in standards organizations) for the backplane bus, and a group of user-defined pins for daughtercard I/O. Homegrown systems usually have a just-as-carefully defined proprietary… Read More

Tag: design rules

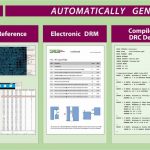

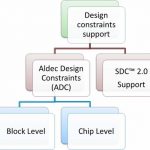

iDRM – A Complete Design Rule Development System

Design rules are at the heart of the interface between the foundry and semiconductor designers, which makes them so critical. Traditionally, design rules and DRC decks have been developed manually with no or little automation. Design rule definitions are written using WORD or other general purpose office tools, and DRC decks… Read More

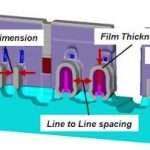

Chips Are Going 3D, DRC Needs to Go 3D Too

The last paradigm shift in DRC was around 0.35um when designs got too large to handle as flat data, and hierarchical approaches were required. Back then the design rules themselves were not that complex, the explosion of data volume came from the complexity of the design itself. But each process node added more design rules intricacies… Read More

Writing the unwritten rules with ALINT-PRO-CDC

EDA verification tools generally do a great job of analyzing the written rules in digital design. Clock domain crossings (CDCs) are more like those unwritten rules in baseball; whether or not you have a problem remains indefinite until later, when retaliation can come swiftly out of nowhere.

Rarely as overt or dramatic as a bench-clearing… Read More