The flexibility of RISC-V processor IP allows much freedom to meet specific requirements – but it also opens the potential for many bugs created during the design process. Advanced processor features are especially prone to errors, increasing the difficulty and time needed for thorough verification. Born out of necessity, … Read More

Tag: design cycle

Importance of Data Management in SoC Verification

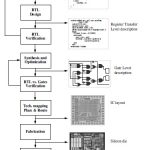

In an era of SoCs with millions of gates, hundreds of IPs and multiple ways to verify designs through several stages of transformations at different levels of hierarchies, it is increasingly difficult to handle such large data in a consistent and efficient way. The hardware and software, and their interactions, have to be consistent… Read More