I am a believer of continuous improvement in anything we do; it’s pleasant to see rapid innovation in technology these days, especially in semiconductor space – technology, design, tools, methodologies… Imagine a 100K gates up to 1M gates design running at a few hundred MHz frequency and at technology node in the range of .18 to … Read More

Tag: catapult

HLS Tools Coming into Limelight!

For about a decade I am looking forward to seeing more of system level design and verification including high level synthesis (HLS), virtual prototyping, and system modeling etc. to come in the main stream of SoC design. Although the progress has been slow, I see it accelerating as more and more tools address the typical pain points… Read More

Designing Hardware with C++ and its Advantages

Very recently, I was seeing intense discussions on the need for agile hardware development just like agile software and ideas were being sought from experts as well as individuals. While in software world it has already evolved, in hardware world it’s yet to see the shift in paradigm. My point is that the end goal of agile hardware… Read More

Expansion at Calypto through Real Value Addition in SoC Design

When we get the notion of expansion of a company, it always provides a positive picture about something good happening to boost that expansion. There can be several reasons for expansion such as merger & acquisition, formation of joint venture or partnership, large customer orders and so on. However, organic expansion which… Read More

Designing the Right Architecture Using HLS

With the advent of HLS tools, general notion which comes to mind is that okay, there’s an automated tool which can optimize your design description written in C++/SystemC and provide you a perfect RTL. In real life, it’s not so, any design description needs hardware designer’s expertise to adopt right algorithm and architecture… Read More

Accelerating SoC Verification Through HLS

Once upon a time there was a struggle for verification completion of semiconductor designs at gate level. Today, beyond imagination, there is a struggle to verify a design with billions of gates at the RTL level which may never complete. The designs are large SoCs with complex architectures and several constraints of area, performance,… Read More

Mark Milligan Joins Calypto. Plus Google at DAC

I talked to Mark Milligan this morning, who has just joined Calypto as VP Marketing. I first met Mark back when he was at CoWare and I was at VaST or maybe it was Virtutech. Then he moved on and ran marketing at SpringSoft which, I’m sure you remember, Synopsys acquired. I asked him what encouraged him to join Calypto.

He said that… Read More

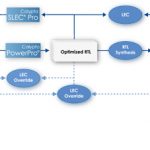

SLEC is Not LEC

One of the questions that Calypto is asked all the time is what is the difference between sequential logical equivalence checking (SLEC) and logical equivalence checking (LEC).

LEC is the type of equivalence checking that has been around for 20 years, although like all EDA technologies gradually getting more powerful. LEC is … Read More

Using HLS to Turbocharge Verification

One of the benefits of using high-level synthesis is obviously the ease of writing some algorithms in SystemC since it is at a higher level than RTL (that’s why we call it high-level synthesis!). But a second benefit is at the verification level. Since a lot of the verification gets done at the SystemC level, less needs to be done at … Read More

Verifying Hardware at the C-level

As more people adopt high-level synthesis (HLS) they start to worry about what is the best design flow to be using. This is especially so for verification since it forms such a large part of the effort on a modern SoC. The more people rely on HLS for producing their RTL from C, the more they realize they had better do a good job of verifying… Read More