You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

I talked to Mark Milligan this morning, who has just joined Calypto as VP Marketing. I first met Mark back when he was at CoWare and I was at VaST or maybe it was Virtutech. Then he moved on and ran marketing at SpringSoft which, I’m sure you remember, Synopsys acquired. I asked him what encouraged him to join Calypto.

He said that… Read More

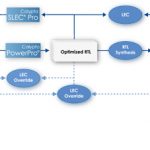

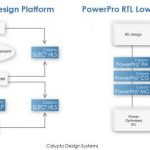

At DVCon today I talked to Sanjiv Kaul, the CEO of Calypto. Just as a reminder, Calypto have 3 products, SLEC (sequential logical equivalence checking, also called sequential formal verification), PowerPro (sequential RTL level power reduction) and Catapult High Level Synthesis (that they took over from Mentor in 2011 in a complicated… Read More

SLEC is Not LECby Paul McLellan on 12-20-2013 at 3:00 pmCategories: EDA

One of the questions that Calypto is asked all the time is what is the difference between sequential logical equivalence checking (SLEC) and logical equivalence checking (LEC).

LEC is the type of equivalence checking that has been around for 20 years, although like all EDA technologies gradually getting more powerful. LEC is … Read More

Mentor is acquiring Oasys, subject to all the usual caveats about shareholder and regulatory approval. The shareholder paperwork went out earlier this week. The common stock is valueless so presumably the price is low (and Mentor historically has not paid high prices for its acquisitions).

So what is going to happen with the technology?… Read More

Major power reductions are possible by reducing power at the RTL and system levels, and not just at the gate and physical level. In fact, as is so often the case in design, changes can have much more impact when done at the higher level, even given that at that point in the design there is less accurate feedback about changes. Later the… Read More

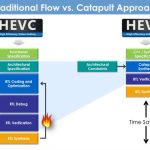

One of the benefits of using high-level synthesis is obviously the ease of writing some algorithms in SystemC since it is at a higher level than RTL (that’s why we call it high-level synthesis!). But a second benefit is at the verification level. Since a lot of the verification gets done at the SystemC level, less needs to be done at … Read More

As more people adopt high-level synthesis (HLS) they start to worry about what is the best design flow to be using. This is especially so for verification since it forms such a large part of the effort on a modern SoC. The more people rely on HLS for producing their RTL from C, the more they realize they had better do a good job of verifying… Read More

Of course if you are in the business of selling high-level synthesis (HLS) tools then the obvious answer is immediately. Start at 9am tomorrow morning. But a more realistic answer is when you are having to do something completely new. If you are working on a legacy design, perhaps with pre-existing IP, then moving the design up to … Read More

Calypto 2013 Reportby Paul McLellan on 07-05-2013 at 5:48 amCategories: EDA

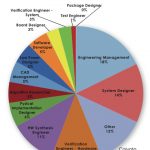

Each year Calypto runs a survey of end-users. This year’s survey and report has two parts, power reduction and high level synthesis (HLS).

The topics covered are:

- survey methodology and demographics

- top methods used to reduce power

- engineering time spent on specfiic RTL tasks to reduce power

- plans to deploy RTL power reduction

…

Read More

This year for DAC, Calypto has assembled an impressive lineup of customer presentation, suite sessions and Designer Tracks. To start with customer presentation, Steve Kommrusch, Fellow Design Engineer from AMD will be giving a talk in the Calypto Suite on AMD’s methodology for low power and will show how AMD was able to get further… Read More